Allen-Bradley

PLC-5 Programmable Controllers

# Instruction Set Reference

#### **Important User Information**

Solid state equipment has operational characteristics differing from those of electromechanical equipment. "Safety Guidelines for the Application, Installation and Maintenance of Solid State Controls" (Publication SGI-1.1) describes some important differences between solid state equipment and hard-wired electromechanical devices. Because of this difference, and also because of the wide variety of uses for solid state equipment, all persons responsible for applying this equipment must satisfy themselves that each intended application of this equipment is acceptable.

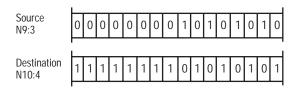

In no event will the Allen-Bradley Company be responsible or liable for indirect or consequential damages resulting from the use or application of this equipment.

The examples and diagrams in this manual are included solely for illustrative purposes. Because of the many variables and requirements associated with any particular installation, the Allen-Bradley Company cannot assume responsibility or liability for actual use based on the examples and diagrams.

No patent liability is assumed by Allen-Bradley Company with respect to use of information, circuits, equipment, or software described in this manual.

Reproduction of the contents of this manual, in whole or in part, without written permission of the Allen-Bradley Company is prohibited.

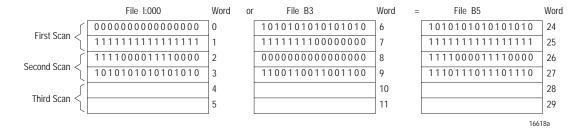

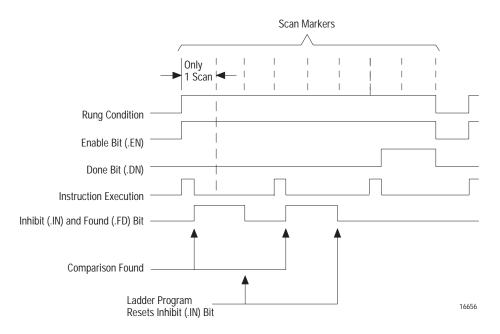

Throughout this manual we use notes to make you aware of safety considerations.

**ATTENTION:** Identifies information about practices or circumstances that can lead to personal injury or death, property damage, or economic loss.

#### Attentions help you:

- · identify a hazard

- avoid the hazard

- recognize the consequences

**Important:** Identifies information that is especially important for successful application and understanding of the product.

Ethemet is a registered trademark of Intel Corporation, Xerox Corporation, and Digital Equipment Corporation.

Data Highway Plus, DH·, PLC, PLC-5, PLC-5/11, -5/20, -5/26, -5/30, -5/40, -5/40L, -5/40L, -5/60L, -5/80, -5/80, -5/20E, -5/40E, and -5/80E are trademarks of Rockwell Automation.

Allen-Bradley is a trademark of Rockwell Automation, a core business of Rockwell International Corporation.

## PLC-5 Instruction Set Alphabetical Listing

| For this<br>Instruction: | See Page:          | For this<br>Instruction: | See Page:         | For this<br>Instruction: | See Page:          |                                       | For this Instruction: | See Page:          |

|--------------------------|--------------------|--------------------------|-------------------|--------------------------|--------------------|---------------------------------------|-----------------------|--------------------|

| ABL                      | 17-5 <sup>1</sup>  | CMP                      | 3-3               | JSR                      | 13-12              | _                                     | RES                   | 2-25               |

| ACB                      | 17-7 <sup>1</sup>  | СОР                      | 9-20              | LBL                      | 13-5               | _                                     | RET                   | 13-12              |

| ACI                      | 17-9 <sup>1</sup>  | COS                      | 4-21 <sup>1</sup> | LEQ                      | 3-9                | _                                     | RTO                   | 2-13               |

| ACN                      | 17-10 <sup>1</sup> | CPT                      | 4-5               | LES                      | 3-10               | _                                     | SBR                   | 13-12              |

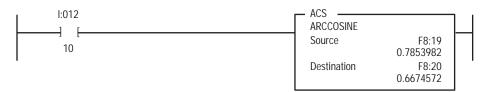

| ACS                      | 4-13 <sup>1</sup>  | CTD                      | 2-20              | LFL                      | 11-5 <sup>1</sup>  | _                                     | SDS                   | 18-2               |

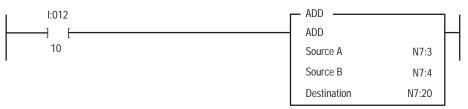

| ADD                      | 4-14               | СТИ                      | 2-18              | LFU                      | 11-5 <sup>1</sup>  | _                                     | SFR                   | 13-23 <sup>1</sup> |

| AEX                      | 17-11 <sup>1</sup> | DDT                      | 10-2              | LIM                      | 3-11               | _                                     | SIN                   | 4-27 <sup>1</sup>  |

| AFI                      | 13-19              | DEG                      | 6-5 <sup>1</sup>  | LN                       | 4-23 <sup>1</sup>  | _                                     | SQI                   | 12-2               |

| AHL                      | 17-12 <sup>1</sup> | DFA                      | 18-3              | LOG                      | 4-24 <sup>1</sup>  | _                                     | SQL                   | 12-2               |

| AIC                      | 17-14 <sup>1</sup> | DIV                      | 4-22              | MCR                      | 13-3               | _                                     | SQ0                   | 12-2               |

| AND                      | 5-2                | DTR                      | 10-8              | MEQ                      | 3-13               | _                                     | SQR                   | 4-28               |

| ARD                      | 17-15 <sup>1</sup> | EOT                      | 13-24             | MOV                      | 7-4                | _                                     | SRT                   | 4-29 <sup>1</sup>  |

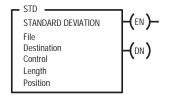

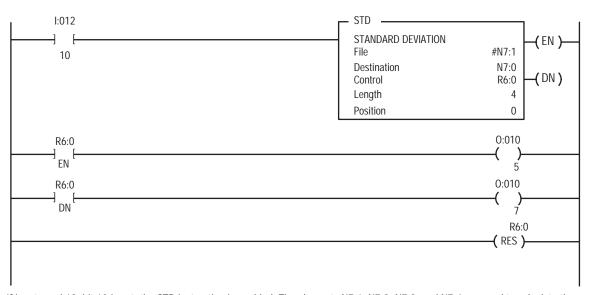

| ARL                      | 17-18 <sup>1</sup> | EQU                      | 3-6               | MSG                      | 16-2               | _                                     | STD                   | 4-31 <sup>1</sup>  |

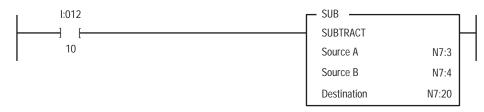

| ASC                      | 17-21 <sup>1</sup> | FAL                      | 9-2               | MUL                      | 4-25               | _                                     | SUB                   | 4-34               |

| ASN                      | 4-15 <sup>1</sup>  | FBC                      | 10-2              | MVM                      | 7-5                | _                                     | TAN                   | 4-35 <sup>1</sup>  |

| ASR                      | 17-22 <sup>1</sup> | FFL                      | 11-5              | NEG                      | 4-26               | _                                     | TND                   | 13-19              |

| ATN                      | 4-16 <sup>1</sup>  | FFU                      | 11-5              | NEQ                      | 3-15               | _                                     | TOD                   | 6-3                |

| AVE                      | 4-17 <sup>1</sup>  | FLL                      | 9-21              | NOT                      | 5-4                | _                                     | TOF                   | 2-9                |

| AWA                      | 17-23 <sup>1</sup> | FOR                      | 13-8              | NXT                      | 13-8               | _                                     | TON                   | 2-5                |

| AWT                      | 17-26 <sup>1</sup> | FRD                      | 6-4               | ONS                      | 13-20              | _                                     | UID                   | 13-25 <sup>1</sup> |

| BRK                      | 13-8               | FSC                      | 9-15              | OR                       | 5-6                | _                                     | UIE                   | 13-26 <sup>1</sup> |

| BSL                      | 11-2               | GEQ                      | 3-7               | OSF                      | 13-22 <sup>1</sup> | _                                     | XIC                   | 1-3                |

| BSR                      | 11-2               | GRT                      | 3-8               | OSR                      | 13-21 <sup>1</sup> | _                                     | XIO                   | 1-4                |

| BTD                      | 7-2                | IDI                      | 1-10 <sup>2</sup> | OTE                      | 1-5                | _                                     | XOR                   | 5-8                |

| BTR                      | 15-4               | IDO                      | 1-11 <sup>2</sup> | OTL                      | 1-6                | _                                     | XPY                   | 4-36 <sup>1</sup>  |

| BTW                      | 15-4               | IIN                      | 1-8               | OTU                      | 1-7                | 1                                     |                       | -5 processors      |

| CIO                      | 15-25 <sup>2</sup> | IOT                      | 1-9               | PID                      | NO TAG             | 2                                     | 0200 program          |                    |

| CLR                      | 4-20               | JMP                      | 13-5              | RAD                      | 6-6 <sup>1</sup>   | with ControlNet PLC-5 processors only |                       |                    |

See Table A for guidelines on choosing the appropriate instruction for the operation you want to perform. Table B lists some examples.

Table A Choosing an Instruction Category

| If You Want to Perform this Operation:  | Use this Instruction Category:                                     |                                    |

|-----------------------------------------|--------------------------------------------------------------------|------------------------------------|

| examine, check or control               | 2-state device or condition multiple 2-state devices or conditions | bit level<br>multi-bit             |

| move, copy, change,<br>compute, compare | analog values, codes<br>multiple sets of values                    | element level<br>file instructions |

| convert                                 | conversion instructions                                            |                                    |

| time or delay                           | timer                                                              |                                    |

| count                                   | counter                                                            |                                    |

| shift or track                          | bit shift                                                          |                                    |

| sequence                                | sequencer                                                          |                                    |

| PID                                     | PID                                                                |                                    |

| message sending/receiving               | message                                                            |                                    |

| transfer data to/from modules           | block transfer or ControlNet transfer                              |                                    |

| diagnostics, fault handling             | diagnostics                                                        |                                    |

| control the flow of your program        | program control                                                    |                                    |

### Table B Example Operations

| If Your Application Calls for Operations such as:        | Use:           |

|----------------------------------------------------------|----------------|

| detecting when a limit switch closes                     | bit level      |

| changing the temperature preset                          | element level  |

| transfer analog data                                     | block transfer |

| turn on a motor 10 seconds after a pump is activated     | timing         |

| move 1 of 3 recipes into a work area                     | multi-element  |

| keep track of parts as they move from station to station | shifting       |

| keep track of total parts in a bin                       | counting       |

## **Summary of Changes**

## New Information Added to this Manual

The list below summarizes the changes that have been made to this manual since the last printing:

| For this Update Information:                                                                        | See Chapter: |

|-----------------------------------------------------------------------------------------------------|--------------|

| Converting non-decimal numbers with the FRD instruction                                             | 6            |

| How non-existing, indirect addresses affect the COP and FLL instructions                            | 9            |

| How the .POS value operates in sequencer instructions                                               | 12           |

| Using a RET instruction                                                                             | 13           |

| Using the PID bias term                                                                             | 14           |

| Using the no zero crossing (.NOZC) and no back calculation (.NOBC) features in the PD control block | 14           |

| Clarification to error code 89 for MSG instruction                                                  | 16           |

| Ethernet PLC-5 processors now support SLC Typed Read and SLC Typed Write MSG instructions           | 16           |

| Configuring a multihop MSG instruction over Ethernet or over ControlNet                             | 16           |

| Monitoring the status of the .EN bit in a continuous MSG instruction                                | 16           |

To help you find new information and updated information in this release of the manual, we have included change bars as shown to the left of this paragraph.

| Summary of Changes |  |  |  |

|--------------------|--|--|--|

|                    |  |  |  |

|                    |  |  |  |

| Notes:             |  |  |  |

#### **Preface**

#### **Conventions**

This manual uses the following conventions:

• Unless otherwise stated:

| References to:                          | Include these Allen-Bradley Processors:                                                                                                                                                                                                                                                                                                    |  |  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Classic PLC-5 processors                | PLC-5/10 <sup>TM</sup> , -5/12 <sup>TM</sup> , -5/15 <sup>TM</sup> , -5/25 <sup>TM</sup> , and -5/VME <sup>TM</sup> processors.                                                                                                                                                                                                            |  |  |

| Enhanced PLC-5 processors               | PLC-5/11 <sup>™</sup> , -5/20 <sup>™</sup> , -5/30 <sup>™</sup> , -5/40 <sup>™</sup> , -5/40 <sup>™</sup> , -5/60 <sup>™</sup> , -5/60L <sup>™</sup> , and -5/80 <sup>™</sup> processors.  Note: Unless otherwise specified, Enhanced PLC-5 processors include Ethernet PLC-5, ControlNet PLC-5, Protected PLC-5 and VME PLC-5 processors. |  |  |

| Ethernet PLC-5 processors               | PLC-5/20E <sup>™</sup> , -5/40E <sup>™</sup> , and -5/80E <sup>™</sup> processors.                                                                                                                                                                                                                                                         |  |  |

| ControlNet PLC-5 processors             | PLC-5/20C <sup>™</sup> , -5/40C <sup>™</sup> , -5/46C <sup>™</sup> , and -5/80C <sup>™</sup> processors.                                                                                                                                                                                                                                   |  |  |

| Protected PLC-5 processors <sup>1</sup> | PLC-5/26 <sup>™</sup> , -5/46 <sup>™</sup> , and -5/86 <sup>™</sup> processors.                                                                                                                                                                                                                                                            |  |  |

| VME PLC-5 processors                    | PLC-5/V30 <sup>™</sup> , -5/V40 <sup>™</sup> , -5/V40L <sup>™</sup> , and -5/V80 <sup>™</sup> processors. See the PLC-5/VME VMEbus Programmable Controllers User Manual for more information.                                                                                                                                              |  |  |

$<sup>^1</sup>$  Protected PLC-5 processors alone do not ensure PLC-5 system security. System security is a combination of the Protected PLC-5 processor, the software, and your application expertise.

• Words in square brackets represent actual keys that you press. For example:

[Enter]; [F1] - Online Programming/Documentation

• Words that describe information that you have to provide are shown in italics. For example, if you have to type a file name, this is shown as:

filename

Messages and prompts that the terminal displays are shown as:

Press a function key

| Preface |  |  |  |

|---------|--|--|--|

|         |  |  |  |

|         |  |  |  |

| Notes:  |  |  |  |

| Relay-Type Instructions            | Chapter 1                         |

|------------------------------------|-----------------------------------|

| (IC, XIO, OTE, OTL, OTU, IIN, IOT, | Using Relay-Type Instructions     |

| DI, IDO                            | I/O Image Files in Data Storage   |

|                                    | Rung Logic                        |

|                                    | Examine On (XIC)1-3               |

|                                    | Examine Off (XIO)1-3              |

|                                    | Energize (OTE)1-4                 |

|                                    | Latch (OTL)                       |

|                                    | Unlatch (OTU)                     |

|                                    | Immediate Input (IIN)             |

|                                    | Immediate Output (IOT)            |

|                                    | Immediate Data Input (IDI)1-8     |

|                                    | Immediate Data Output (IDO)       |

|                                    | Using IDI and IDO Instructions    |

| Timer Instructions TON, TOF,       | Chapter 2                         |

| RTO Counter Instructions CTU,      | Using Timers and Counters         |

| CTD Reset RES                      | Using Timers                      |

| TO ROSOT RES                       | Entering Parameters               |

|                                    | Timer Accuracy                    |

|                                    | Timer On Delay (TON)              |

|                                    | Using Status Bits                 |

|                                    | Timer Off Delay (TOF)2-7          |

|                                    | Using Status Bits                 |

|                                    | Retentive Timer On (RTO)2-10      |

|                                    | Using Status Bits                 |

|                                    | Using Counters                    |

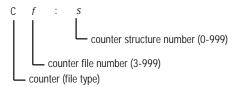

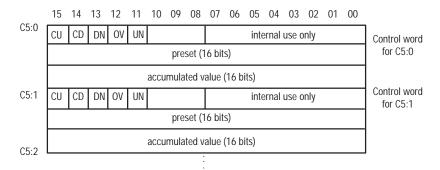

|                                    | Entering Parameters               |

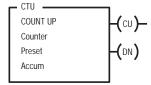

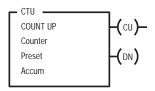

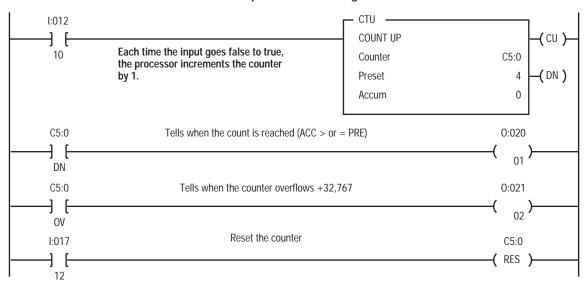

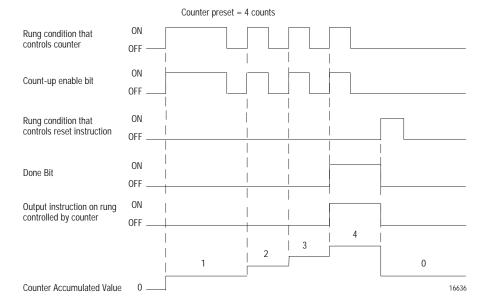

|                                    | Count Up (CTU)                    |

|                                    | Using Status Bits                 |

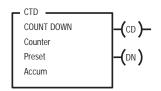

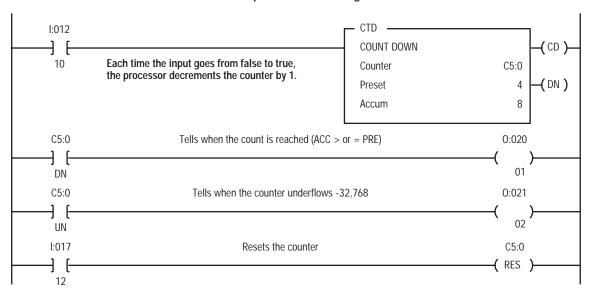

|                                    | Count Down (CTD)                  |

|                                    | Using Status Bits                 |

|                                    | Timer and Counter Reset (RES)2-20 |

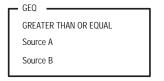

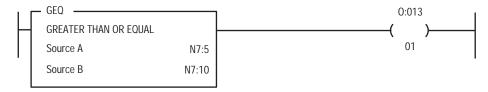

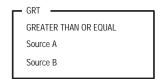

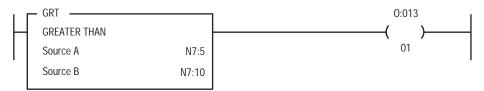

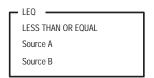

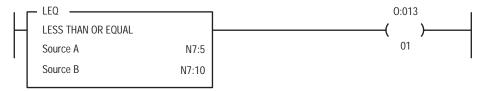

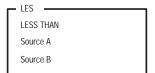

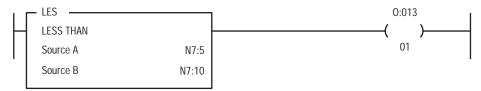

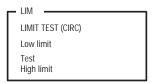

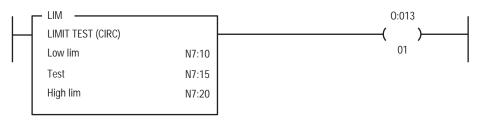

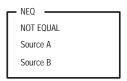

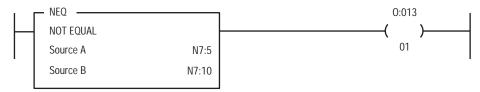

| Compare Instructions<br>CMP, EQU, GEQ, GRT, LEQ, LES, LIM,<br>MEQ, NEQ                                                 | Chapter 3 Using Compare Instructions. Using Arithmetic Status Flags Compare (CMP). Entering the CMP Expression. Determining the Length of an Expression. Equal to (EQU). Greater than or Equal to (GEQ). Greater than (GRT) Less than or Equal to (LEQ). Less than (LES) Limit Test (LIM). Entering Parameters Mask Compare Equal to (MEQ)                                                                              | 3-2<br>3-2<br>3-3<br>3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7                                       |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

|                                                                                                                        | Entering Parameters                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                   |

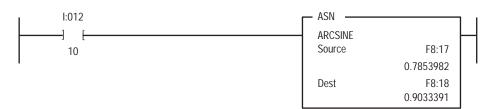

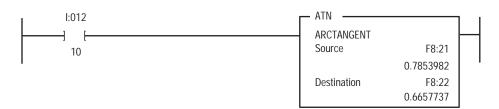

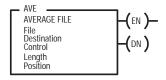

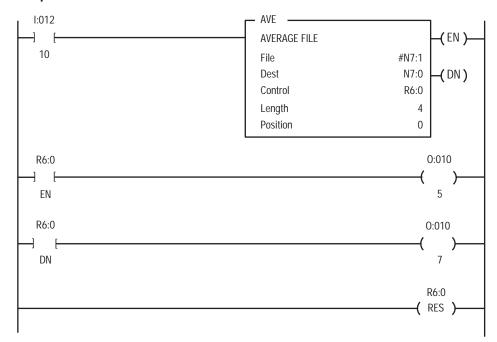

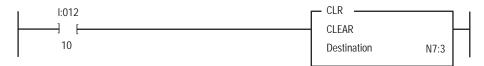

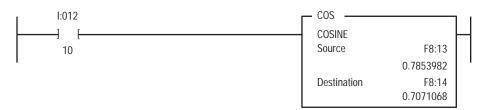

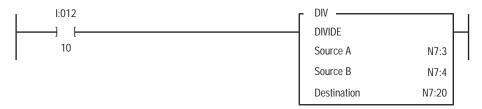

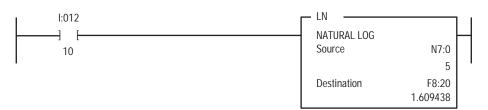

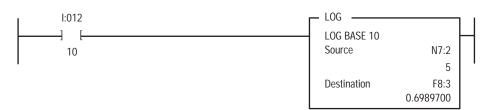

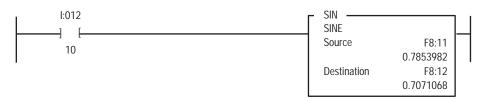

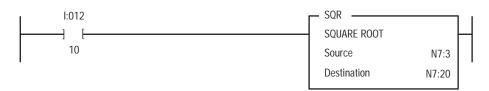

| Compute Instructions CPT, ACS, ADD, ASN, ATN, AVE, CLR, COS, DIV, LN, LOG, MUL, NEG, SIN, SRT, SQR, STD, SUB, TAN, XPY | Chapter 4 Using Compute Instructions. Using Arithmetic Status Flags Data Types and the Compute Instruction Using Floating Point Data Types Compute (CPT) Entering the CPT Expression Determining the Length of an Expression. Determining the Order of Operation Expression Examples. Entering the Destination Using CPT Functions Arc Cosine (ACS) Addition (ADD) Arc Sine (ASN). Arc Tangent (ATN) Average File (AVE) | 4-2<br>4-3<br>4-4<br>4-5<br>4-5<br>4-7<br>4-8<br>4-9<br>4-9<br>4-11<br>. 4-12<br>. 4-13<br>. 4-14 |

|                                                                                                                        | Entering Parameters Using Status Bits Clear (CLR) Cosine (COS) Divide (DIV) Natural Log (LN) Log to the Base 10 (LOG). Multiply (MUL) Negate (NEG). Sine (SIN) Square Root (SQR).                                                                                                                                                                                                                                       | . 4-15<br>. 4-16<br>. 4-17<br>. 4-18<br>. 4-19<br>. 4-20<br>. 4-21<br>. 4-22<br>. 4-23            |

Table of Contents toc–3

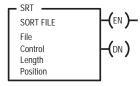

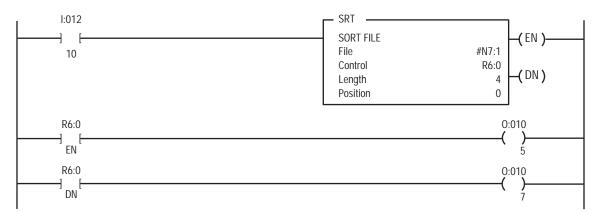

|                                                     | Sort File (SRT)                                                                                                                                                                                                   | -26<br>-27<br>-28<br>-29<br>-29<br>-31<br>-32 |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Logical Instructions<br>AND, NOT, OR, XOR           | Chapter 5 Using Logical Instructions Using Arithmetic Status Flags AND Operation (AND). NOT Operation (NOT). OR Operation (OR). Exclusive OR Operation (XOR)                                                      | 5-1<br>5-2<br>5-3<br>5-4                      |

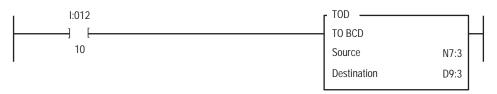

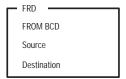

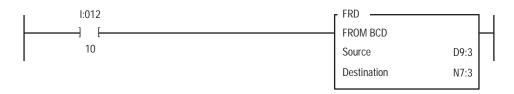

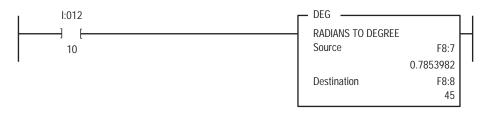

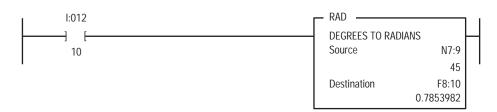

| Conversion Instructions<br>FRD and TOD, DEG and RAD | Chapter 6 Using the Conversion Instructions Using Arithmetic Status Flags Convert to BCD (TOD) Convert from BCD (FRD) Degree (DEG) (Enhanced PLC-5 Processors Only) Radian (RAD) (Enhanced PLC-5 Processors Only) | 6-1<br>6-2<br>6-2<br>6-3                      |

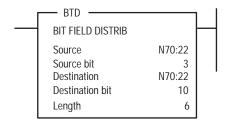

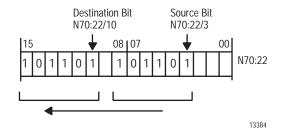

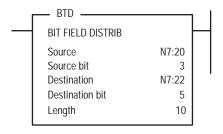

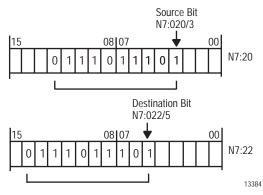

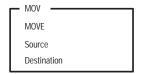

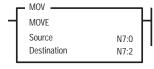

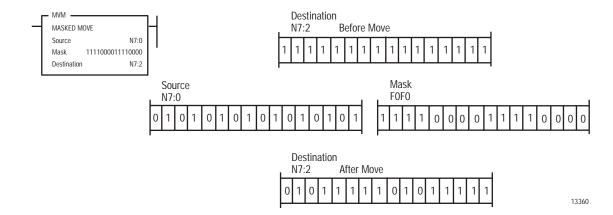

| Bit Modify and Move Instructions<br>BTD, MOV, MVM   | Chapter 7 Using Bit Modify and Move Instructions Bit Distribute (BTD) Entering Parameters Move (MOV) Masked Move (MVM). Entering Parameters                                                                       | 7-2<br>7-2<br>7-3<br>7-4                      |

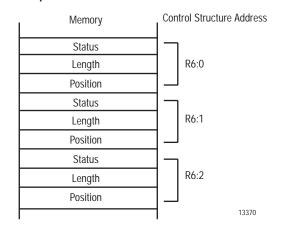

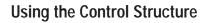

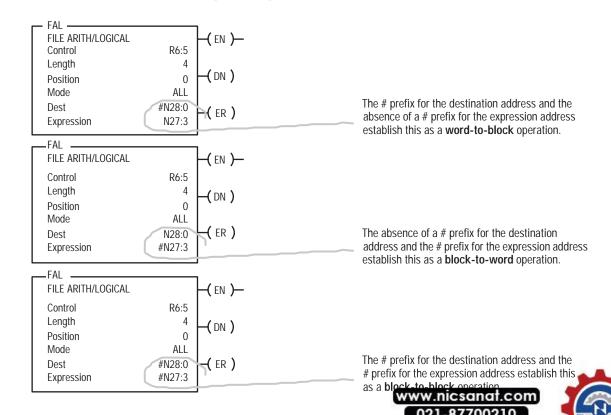

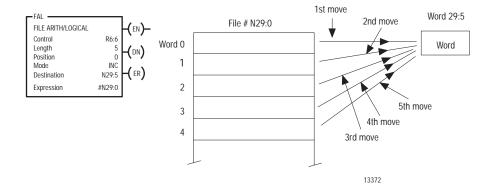

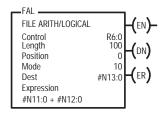

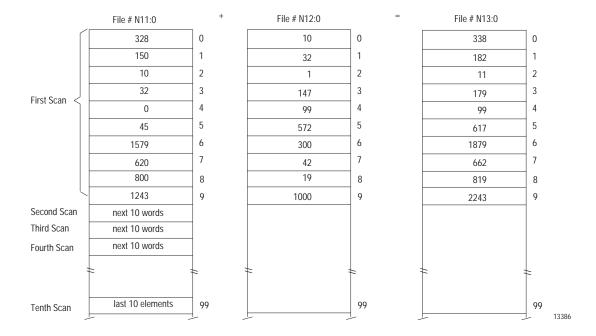

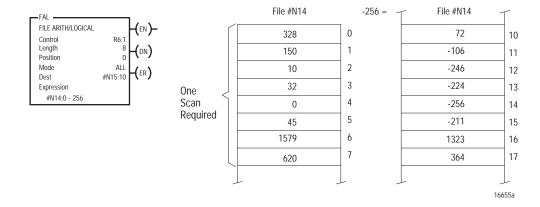

| File Instruction Concepts                           | Chapter 8 Concepts of File Operation Entering Parameters Using the Control Structure Manipulating File Data. Choosing Modes of Block Operation All Mode Numerical Mode Incremental Mode                           | 8-1<br>8-2<br>8-3<br>8-5<br>8-5<br>8-6        |

|                                                     | Special Case, Numerical Mode with Words Per Scan = 1                                                                                                                                                              | გ_გ                                           |

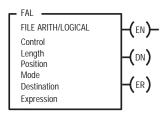

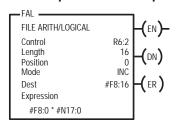

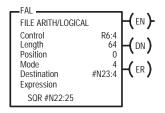

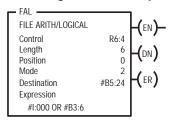

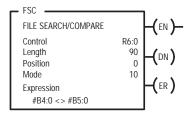

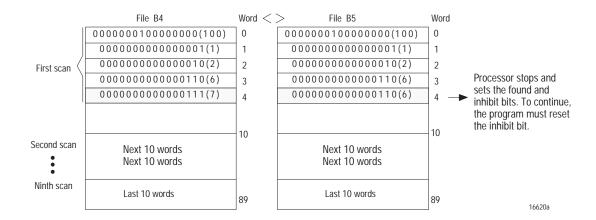

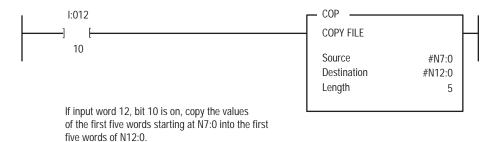

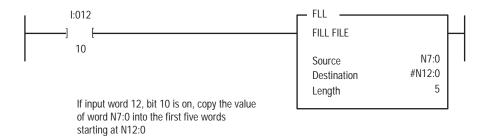

| File Instructions FAL, FSC, COP, FLL                        | Chapter 9 Using File Instructions                                                                                                                                                                                                                                         |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                             | File Fill (FLL)                                                                                                                                                                                                                                                           |

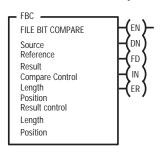

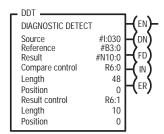

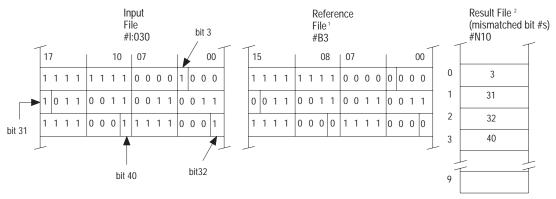

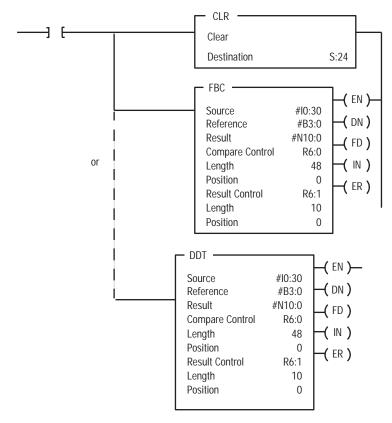

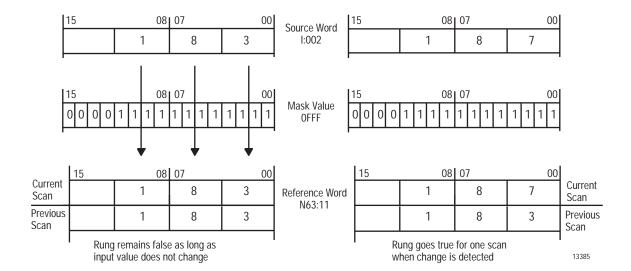

| Diagnostic Instructions<br>FBC, DDT, DTR                    | Chapter 10Using Diagnostic Instructions10-1File Bit Comparison (FBC) and Diagnostic Detect (DDT)10-2Selecting the Search Mode10-2One Mismatch at a Time10-2All Per Scan10-3Entering Parameters10-4Using Status Bits10-5Data Transitional (DTR)10-8Entering Parameters10-8 |

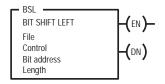

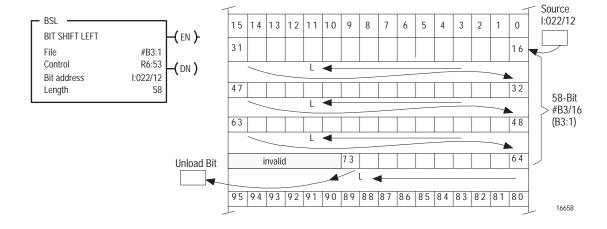

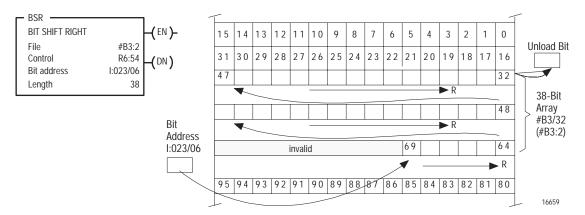

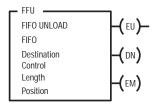

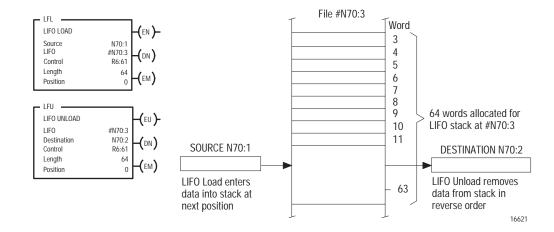

| Shift Register Instructions<br>BSL, BSR, FFL, FFU, LFL, LFU | Chapter 11Applying Shift Registers11-1Using Bit Shift Instructions11-2Entering Parameters11-2Using Status Bits11-3Using FIFO and LIFO Instructions11-5Entering Parameters11-5Using Status Bits11-6                                                                        |

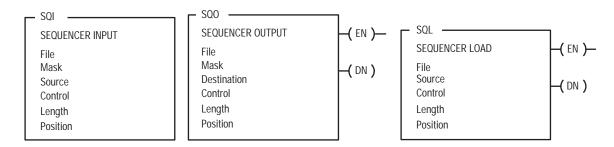

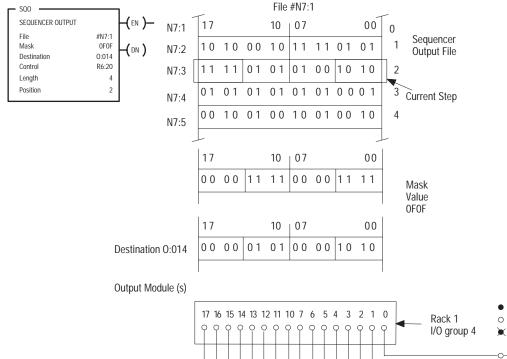

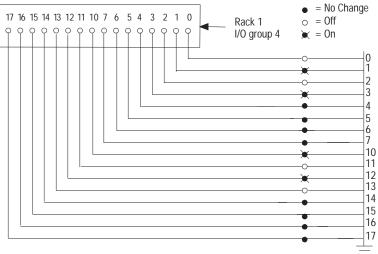

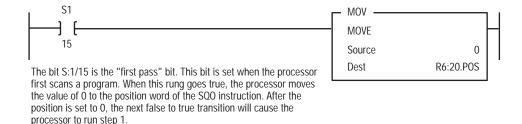

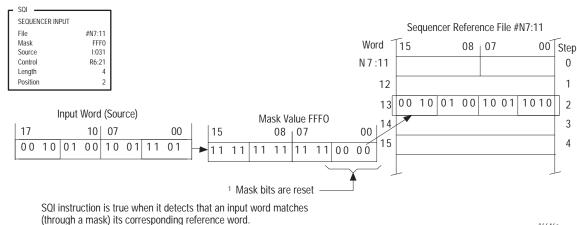

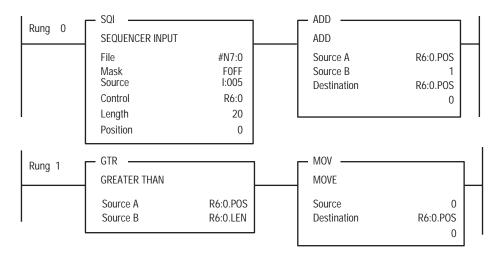

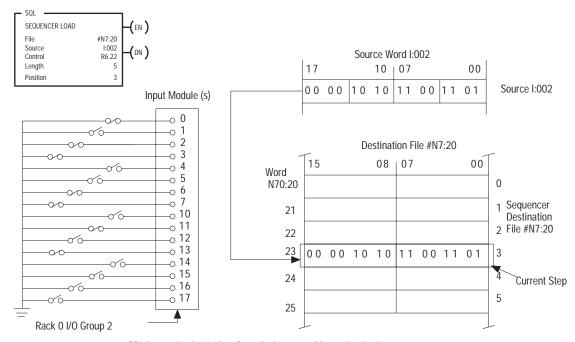

| Sequencer Instructions<br>SQ0, SQI, SQL                     | Chapter 12Applying Sequencers12-1Using Sequencer Instructions12-2Entering Parameters12-2Using Status Bits12-4Resetting the Position of SQO12-6Using SQI Without SQO12-7                                                                                                   |

Table of Contents toc-5

| Program Control Instructions MCR  |

|-----------------------------------|

| JMP, LBL, FOR, NXT, BRK, JSR,     |

| SBR, RET, TND, AFI, ONS, OSR, OSF |

| SFR, EOT, UIE, UID                |

| Chapter 13                                          |       |

|-----------------------------------------------------|-------|

| Selecting Program Flow Instructions                 |       |

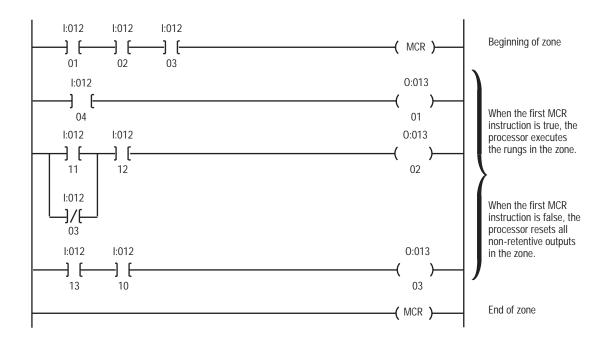

| Master Control Reset (MCR)                          |       |

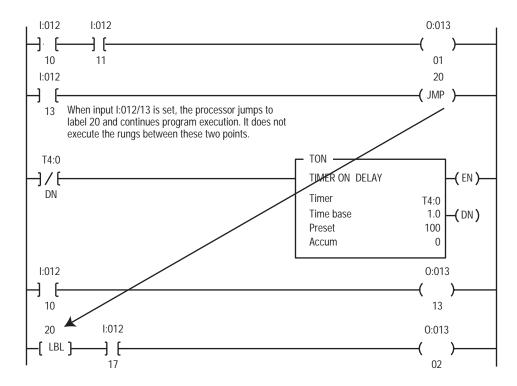

| Jump (JMP) and Label (LBL)                          |       |

| Using JMP                                           |       |

| Using LBL                                           |       |

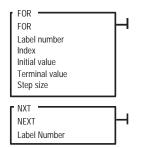

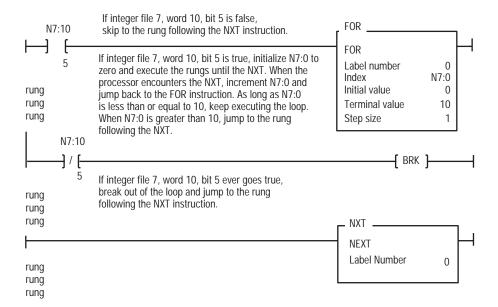

| For Next Loop (FOR, NXT), Break (BRK)               |       |

| Entering Parameters                                 |       |

| Using FOR                                           |       |

| Using BRK                                           |       |

| Using NXT                                           | 13-7  |

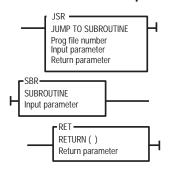

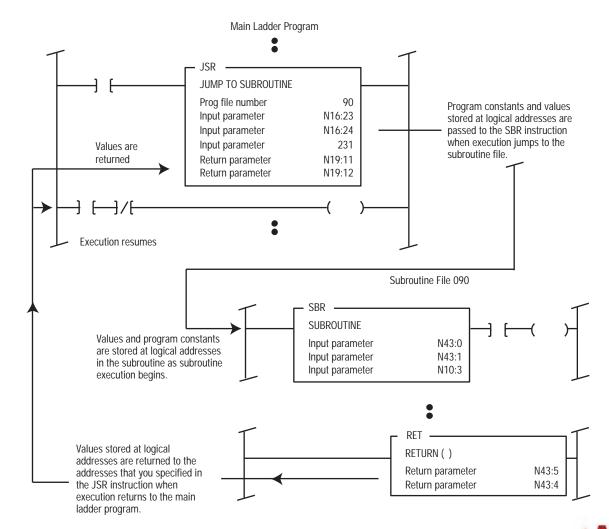

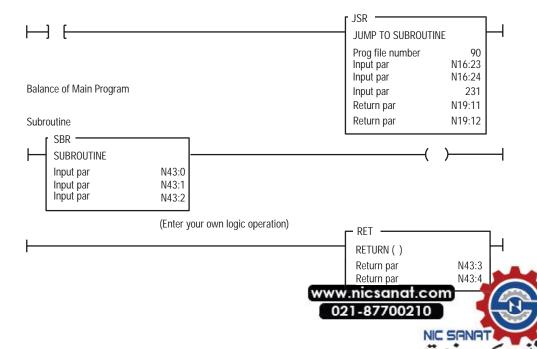

| Jump to Subroutine (JSR), Subroutine (SBR),         |       |

| and Return (RET)                                    |       |

| Passing Parameters                                  |       |

| Entering Parameters                                 |       |

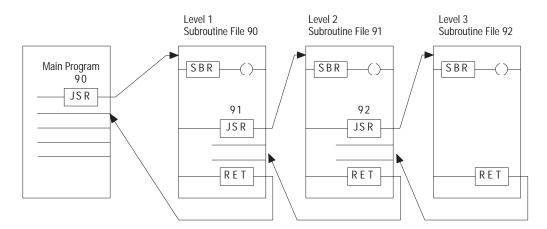

| Nesting Subroutine Files                            |       |

| Using JSR                                           |       |

| Using SBR                                           |       |

| Using RET                                           |       |

| Temporary End (TND)                                 |       |

| Always False (AFI)                                  |       |

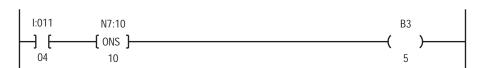

| One Shot (ONS)                                      |       |

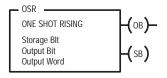

| One Shot Rising (OSR)                               |       |

| Entering Parameters                                 |       |

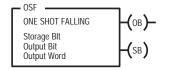

| One Shot Falling (OSF)                              |       |

| Entering Parameters                                 |       |

| Sequential Function Chart Reset (SFR)               |       |

| Entering Parameters                                 |       |

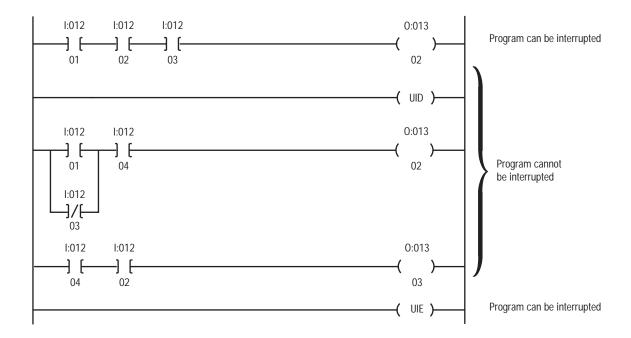

| User Interrupt Disable (UID)                        |       |

| User Interrupt Enable (UIE)                         |       |

| osci interrupt Enable (off)                         | 13 20 |

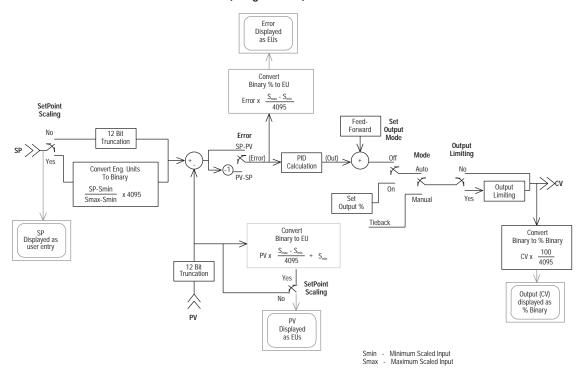

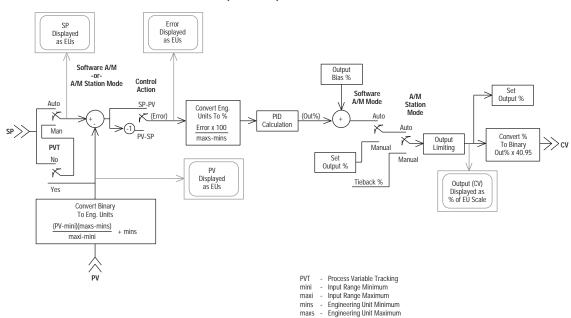

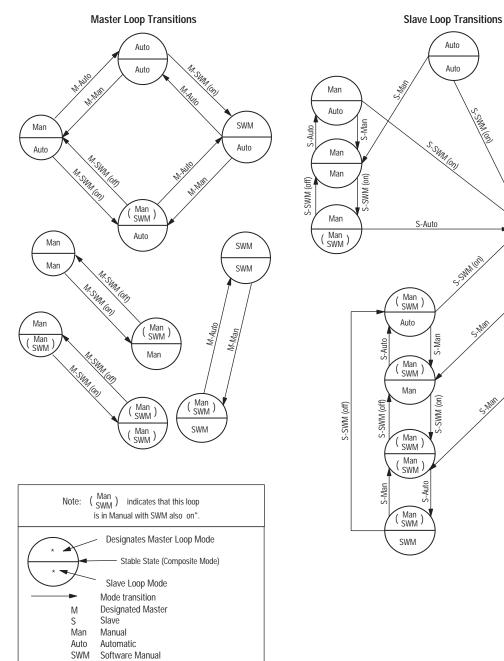

| Chapter 14                                          |       |

| Using PID                                           | 14-1  |

| PID Features                                        | 14-2  |

| Using PID Equations                                 |       |

| Conversion of Gain Constants                        | 14-3  |

| Integral Term Implementation                        | 14-3  |

| Derivative Term                                     | 14-4  |

| Setting Input/Output Ranges                         |       |

| Implementing Scaling to Engineering Units           | 14-5  |

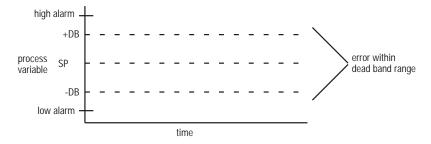

| Setting the Dead Band                               |       |

| Using Zero-Crossing                                 |       |

| Using No Zero Crossing                              |       |

| Selecting the Derivative Term (Acts on PV or Error) | 14-7  |

**Process Control Instruction PID**

| Setting Output Alarms                                 | 14-7    |

|-------------------------------------------------------|---------|

| Using Output Limiting                                 | 14-7    |

| Anti-Reset Windup                                     | 14-8    |

| Using a Manual Mode Operation (Bumpless Transfer) .   | 14-8    |

| Set Output                                            | 14-8    |

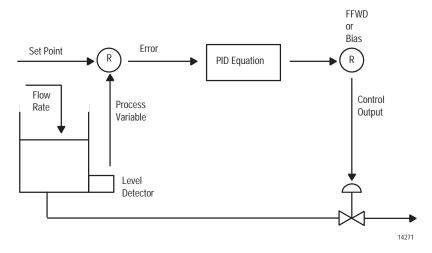

| Feedforward or Output Biasing                         | 14-9    |

| Resume Last State                                     |         |

| PID Instruction                                       | . 14-10 |

| Using No Back Calculation                             | . 14-11 |

| Operational Status Bits                               | . 14-11 |

| Integer Block                                         | . 14-11 |

| PD Block                                              |         |

| Entering Parameters                                   |         |

| Using an Integer Data File Type for the Control Block |         |

| Using Control Block Values                            |         |

| Using a PD File Type for the Control Block            |         |

| Using Control Block Values                            |         |

| Programming Considerations                            |         |

| Run Time Errors                                       |         |

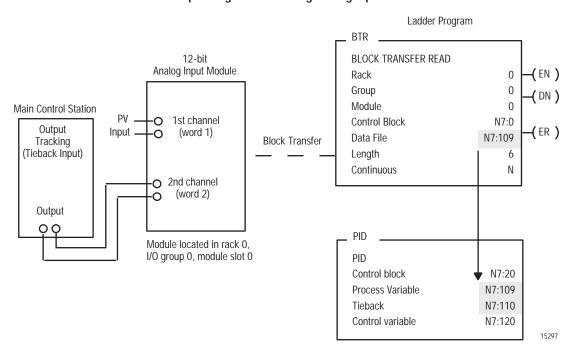

| Transferring Data to the PID Instruction              | . 14-25 |

| Loop Considerations                                   |         |

| Number of PID Loops                                   |         |

| Loop Update Time                                      |         |

| Descaling Inputs                                      |         |

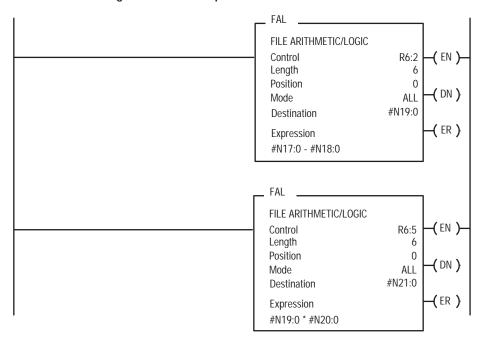

| PID Examples                                          |         |

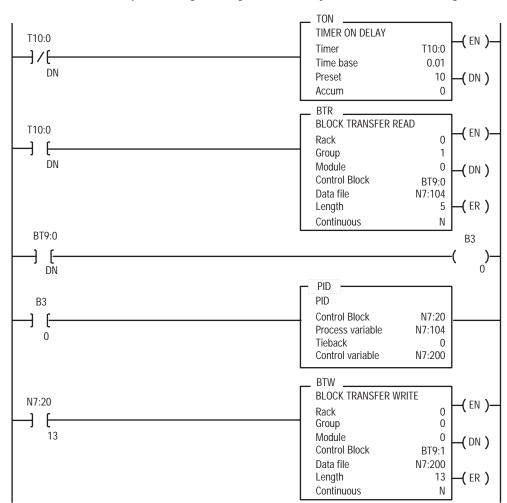

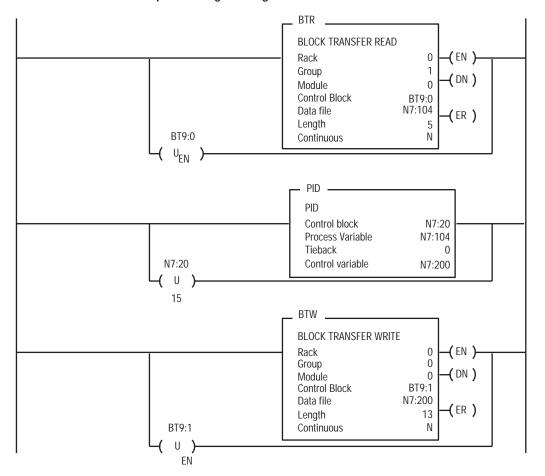

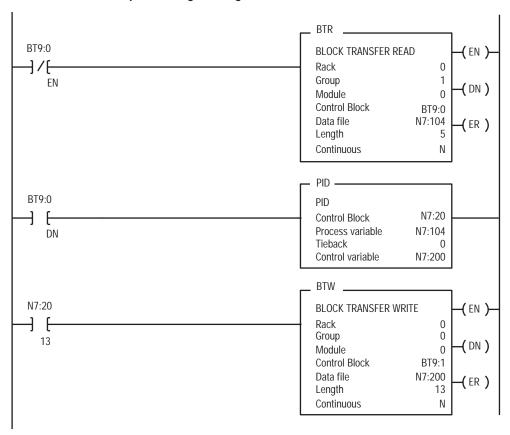

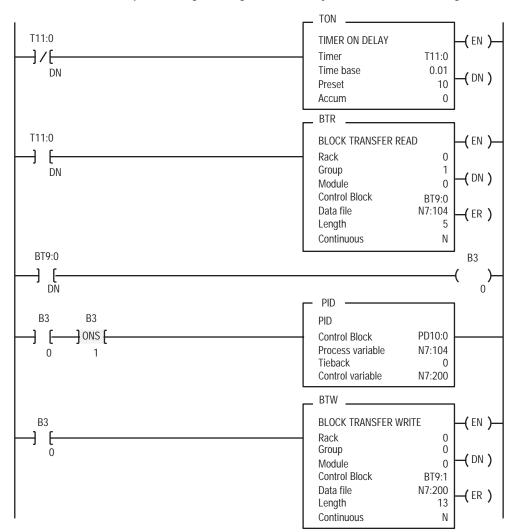

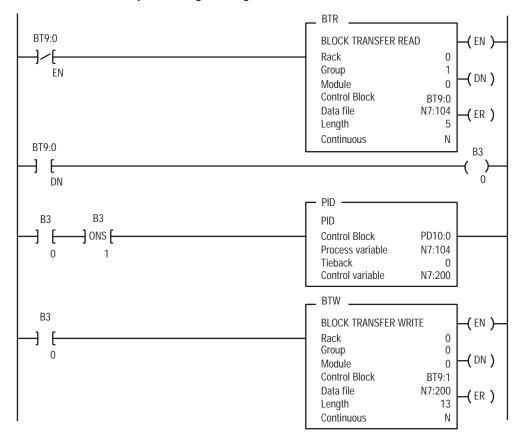

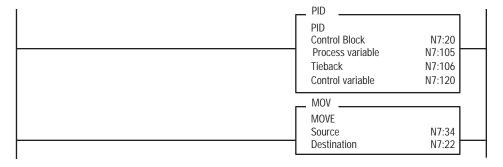

| Integer Block (N) Examples                            | . 14-29 |

| Main Program File                                     |         |

| STI Program File                                      |         |

| RTS Program File                                      |         |

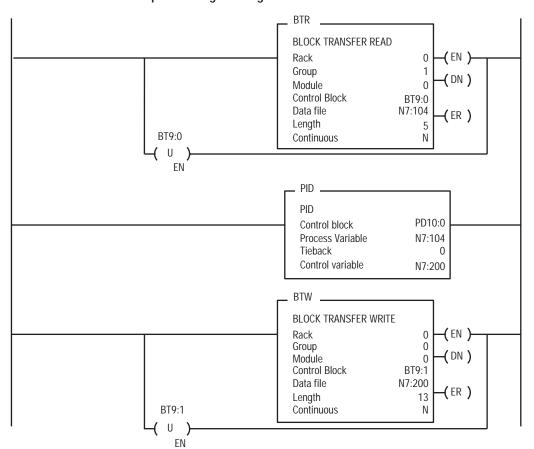

| PD Block Examples                                     |         |

| Main Program File                                     |         |

| STI Program File                                      |         |

| RTS Program File                                      |         |

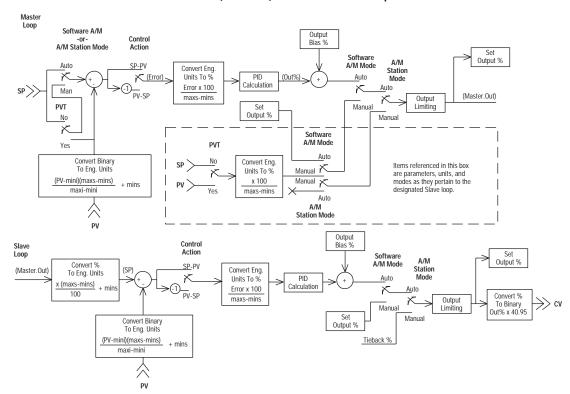

| Ladder Logic Simulation of a Manual Control Station   |         |

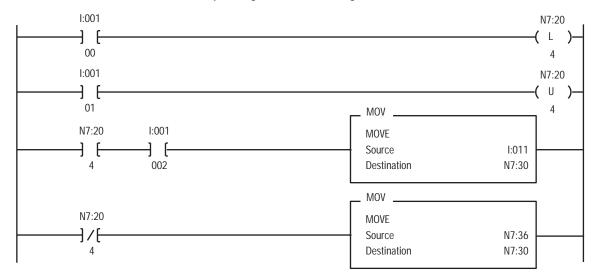

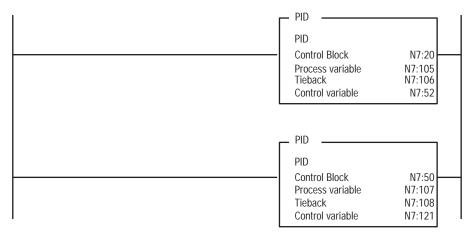

| Cascading Loops                                       |         |

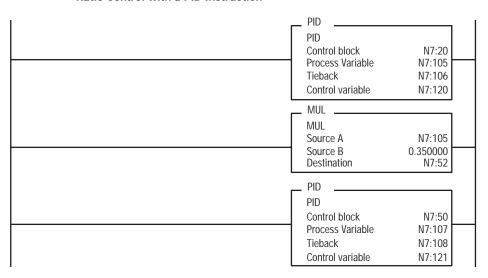

| Ratio Control                                         |         |

| Process Variable Tracking                             |         |

| PID Theory                                            |         |

Table of Contents toc–7

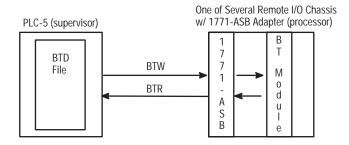

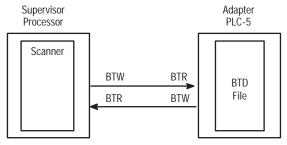

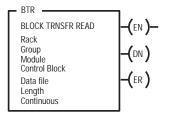

| Block-Transfer Instructions    |

|--------------------------------|

| BTR and BTW and ControlNet I/O |

| Transfer Instruction CIO       |

| Chapter 15                                                     |

|----------------------------------------------------------------|

| Using Block Transfer and ControlNet I/O                        |

| Transfer Instructions                                          |

| Using Block Transfer Instructions                              |

| Block-Transfer Read (BTR) and Block-Transfer Write (BTW). 15-3 |

| Block-Transfer Request Queue                                   |

| Entering Parameters                                            |

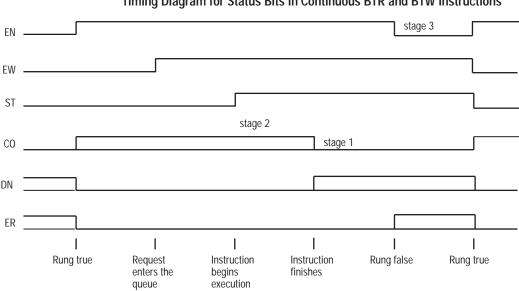

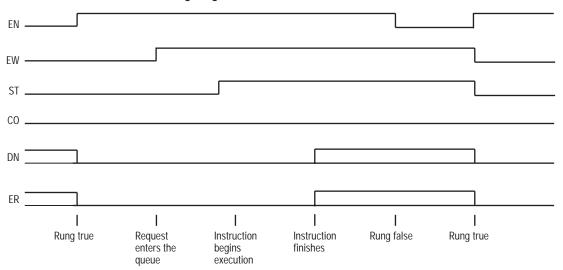

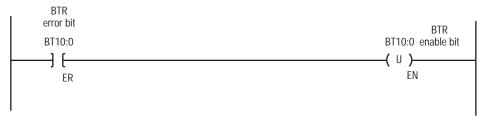

| Using Status Bits15-6                                          |

| Using the Control Block                                        |

| Requested Word Count (.RLEN)                                   |

| Transmitted Word Count (.DLEN)                                 |

| File Number (.FILE)                                            |

| Element Number (.ELEM)15-9                                     |

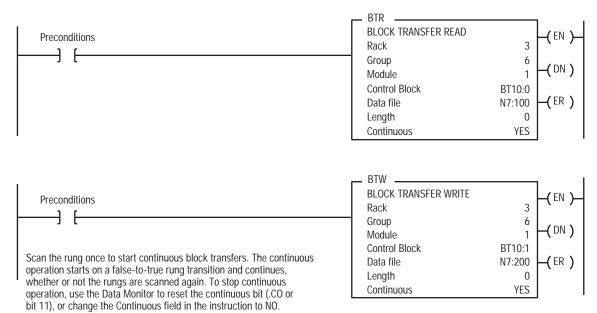

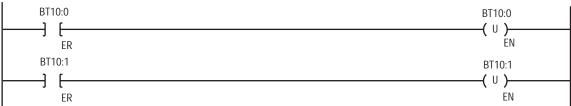

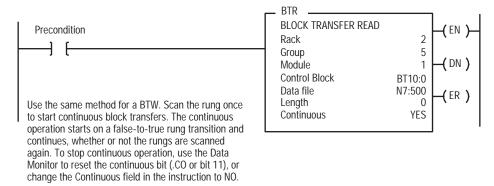

| Selecting Continuous Operation                                 |

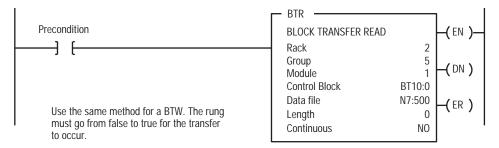

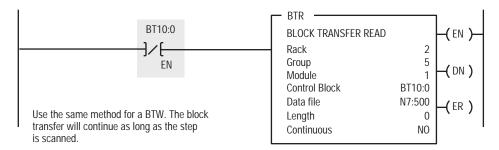

| Selecting Non-Continuous Operation                             |

| Block Transfer Timing – Classic PLC-5 Processors 15-13         |

| Instruction Run Time                                           |

| Waiting Time in the Queue                                      |

| Transfer Time                                                  |

| Block Transfer Timing – Enhanced PLC-5 Processors 15-14        |

| Instruction Run Time                                           |

| Waiting Time in the Holding Area15-14                          |

| Transfer Time                                                  |

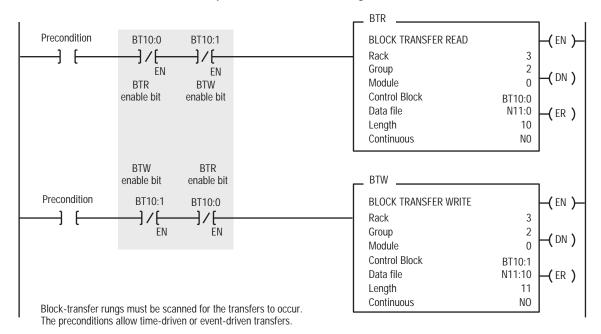

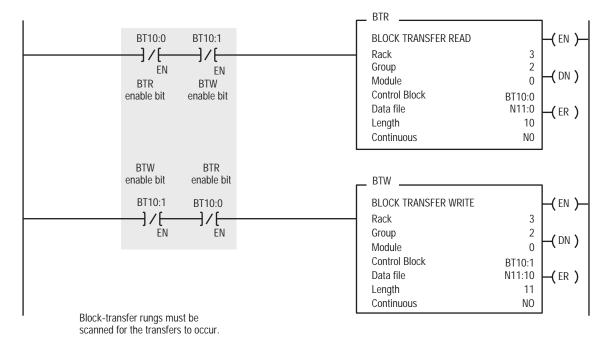

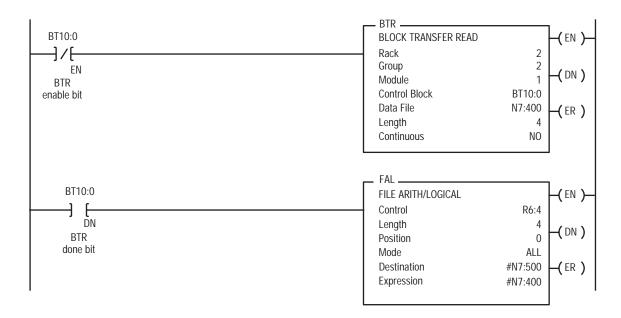

| Programming Examples                                           |

| Example Bidirectional Alternating Block-Transfer 15-16         |

| Example Bidirectional Alternating Repeating                    |

| Block-Transfer                                                 |

| Example Bidirectional Continuous Block-Transfer 15-18          |

| Example Directional Non-Continuous Block-Transfer 15-19        |

| Example Directional Repeating Block Transfer 15-19             |

| Example Directional Continuous Block-Transfer 15-20            |

| Example Buffering Block Transfer-Data 15-21                    |

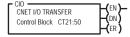

| ControlNet I/O Transfer (CIO) Instruction 15-22                |

| Control Block Address                                          |

| Using the CIO Instruction                                      |

| Using Status Bits                                              |

| Using the CT Central Block 15-25                               |

| Message Instruction MSG | Chapter 16                                                 |      |

|-------------------------|------------------------------------------------------------|------|

| 3                       | Using the Message Instruction                              | 16-1 |

|                         | Message (MSG)                                              |      |

|                         | Entering Parameters                                        | 16-2 |

|                         | Control Block Address                                      |      |

|                         | MSG Data Entry Screen                                      | 16-3 |

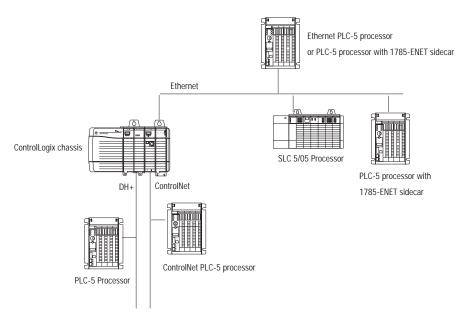

|                         | Using the Message Instruction for Ethernet                 |      |

|                         | Communications                                             | 16-5 |

|                         | Entering Parameters                                        | 16-5 |

|                         | Using the Message Instruction for PLC-5 Ethernet Interface |      |

|                         | Module Communications                                      | 16-7 |

|                         | Entering Parameters                                        | 16-7 |

|                         | Configuring an Ethernet Multihop MSG Instruction           | 16-9 |

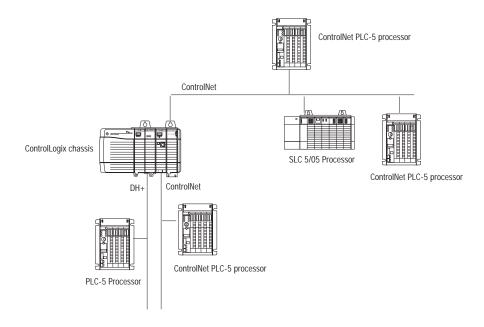

|                         | Using the Message Instruction for ControlNet               |      |

|                         | Communications                                             | 5-10 |

|                         | Control Block Address                                      | 5-10 |

|                         | Configuring a ControlNet Multihop MSG Instruction 16       | 5-11 |

|                         | Using Status Bits16                                        |      |

|                         | Using the Control Block                                    | 5-13 |

|                         | Error Code (.ERR)                                          | 5-13 |

|                         | Requested Length (.RLEN)16                                 | 5-13 |

|                         | Transmitted Length (.DLEN)                                 | 5-13 |

|                         | Entering Parameters                                        | 5-14 |

|                         | Communication Command                                      |      |

|                         | External Data Table Addresses                              | 5-15 |

|                         | PLC-2 to PLC-5 Compatibility Files                         | 5-15 |

|                         | Sending SLC Typed Logical Read and Typed Logical           |      |

|                         | Write Commands                                             | 5-16 |

|                         | Monitoring a Message Instruction                           | 5-17 |

|                         | Selecting Continuous Operation                             |      |

|                         | Selecting Non-Continuous Operation                         |      |

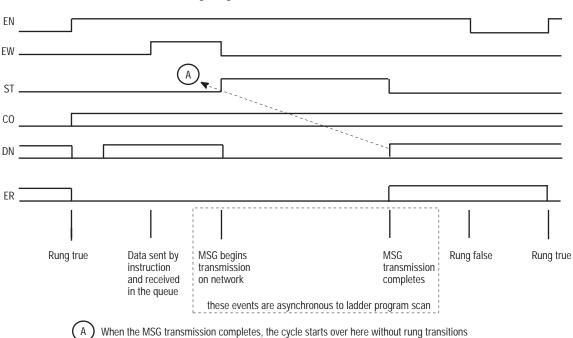

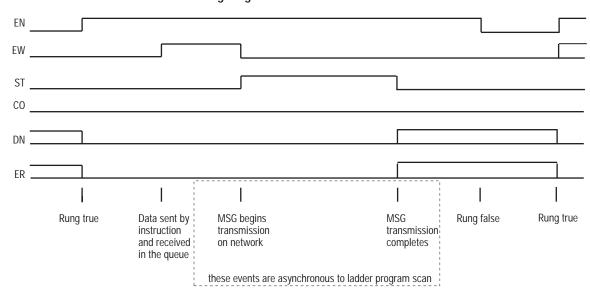

|                         | MSG Timing16                                               | 5-20 |

Table of Contents toc-9

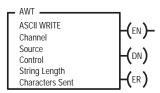

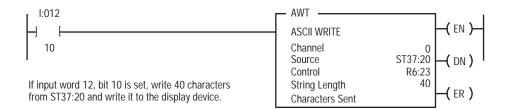

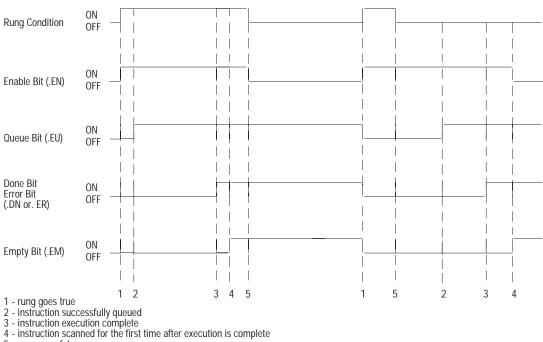

| ASCII Instructions                 | Chapter 17 Using ASCII Instructions         |         |

|------------------------------------|---------------------------------------------|---------|

| ABL, ACB, ACI, ACN, AEX, AIC, AHL, | Enhanced PLC-5 Processors Only              | 17-1    |

| ARD, ARL, ASC, ASR, AWA, AWT       | Using Status Bits                           |         |

|                                    | Using the Control Block                     |         |

|                                    | Length (.LEN).                              |         |

|                                    | Position (.POS)                             |         |

|                                    | Using Strings                               |         |

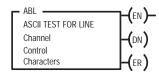

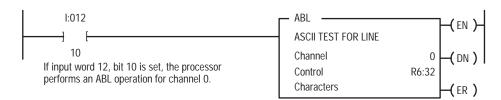

|                                    | Test Buffer for Line (ABL)                  |         |

|                                    | Entering Parameters                         |         |

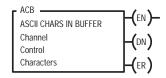

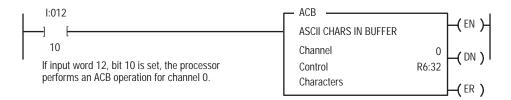

|                                    | Number of Characters in Buffer (ACB)        |         |

|                                    | Entering Parameters                         |         |

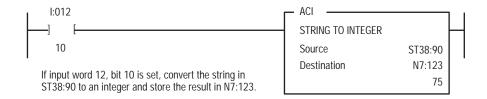

|                                    | ASCII String to Integer (ACI)               |         |

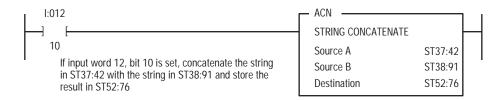

|                                    | ASCII String Concatenate (ACN)              |         |

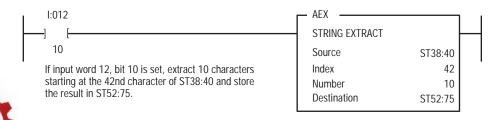

|                                    | ASCII String Extract (AEX)                  |         |

|                                    | Entering Parameters                         |         |

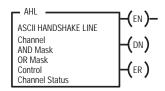

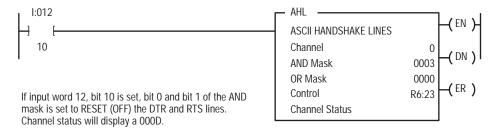

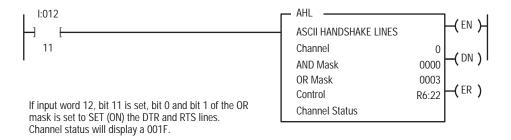

|                                    | ASCII Set or Reset Handshake Lines (AHL)    |         |

|                                    | Entering Parameters                         |         |

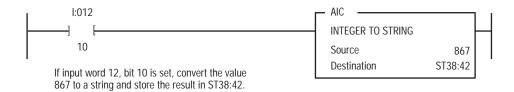

|                                    | ASCII Integer to String (AIC)               | 17-9    |

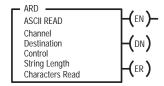

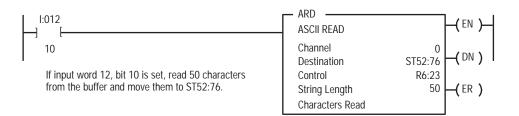

|                                    | ASCII Read Characters (ARD)                 |         |

|                                    | Entering Parameters                         | . 17-10 |

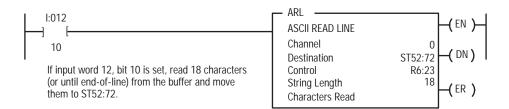

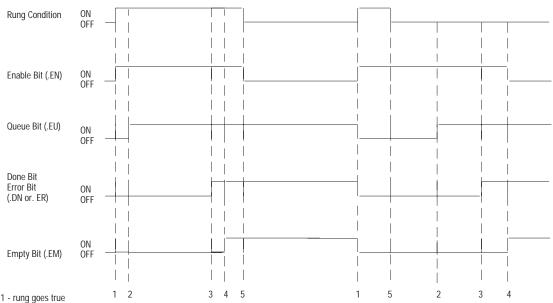

|                                    | ASCII Read Line (ARL)                       | . 17-12 |

|                                    | Entering Parameters                         | . 17-12 |

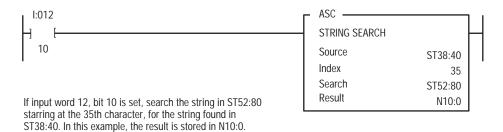

|                                    | ASCII String Search (ASC)                   | . 17-14 |

|                                    | Entering Parameters                         | . 17-14 |

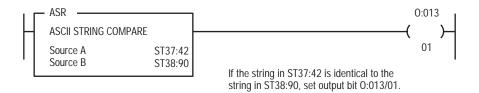

|                                    | ASCII String Compare (ASR)                  |         |

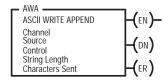

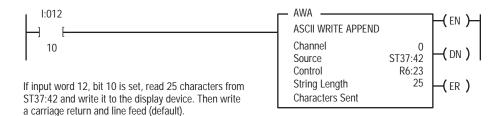

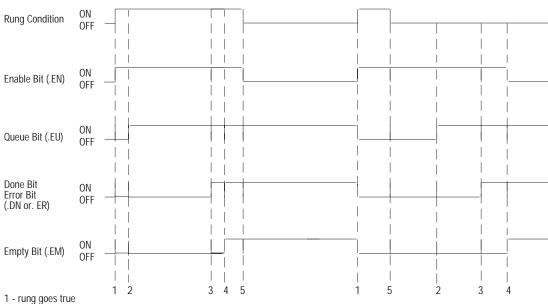

|                                    | ASCII Write with Append (AWA)               |         |

|                                    | Entering Parameters                         |         |

|                                    | ASCII Write (AWT)                           |         |

|                                    | Entering Parameters                         | . 17-17 |

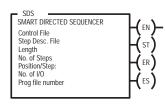

| Custom Application Routine         | Chapter 18                                  |         |

| Instructions SDS, DFA              | Chapter Objectives                          |         |

|                                    | Smart Directed Sequencer (SDS) Overview     |         |

|                                    | Programming the SDS Instruction             |         |

|                                    | Diagnostic Fault Annunciator (DFA) Overview |         |

|                                    | Programming the DFA Instruction             | 18-3    |

| Instruction Timing and Memory Requirements   | Appendix A-1 Instruction Timing and Memory Requirements                                                                                                                                                                                                                                                                                                                                                                                             |  |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                              | Additional Timing Considerations: Classic PLC-5 Processors                                                                                                                                                                                                                                                                                                                                                                                          |  |

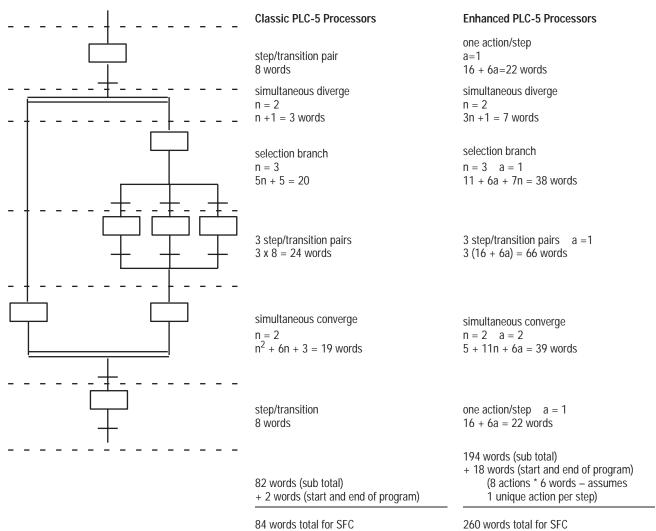

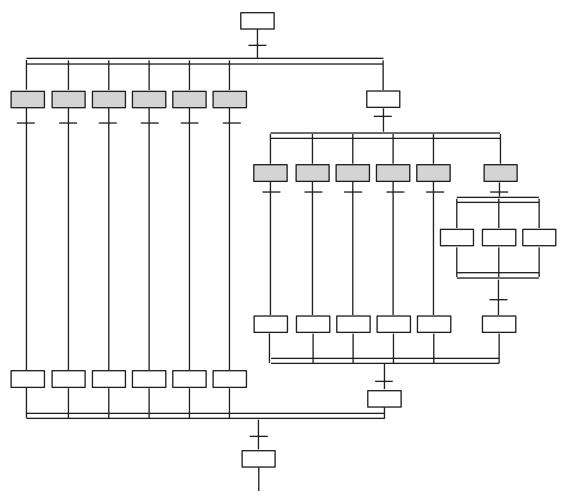

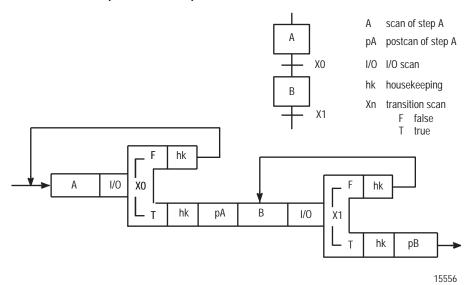

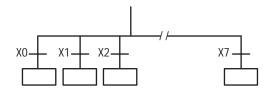

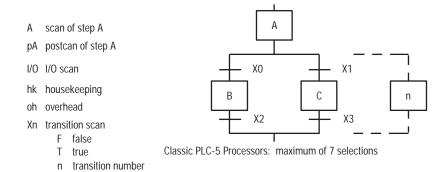

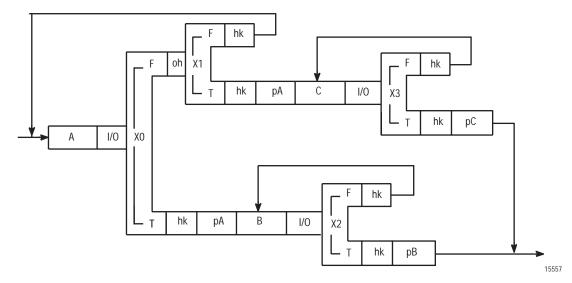

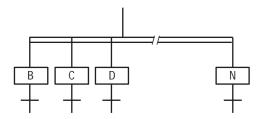

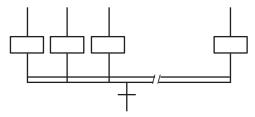

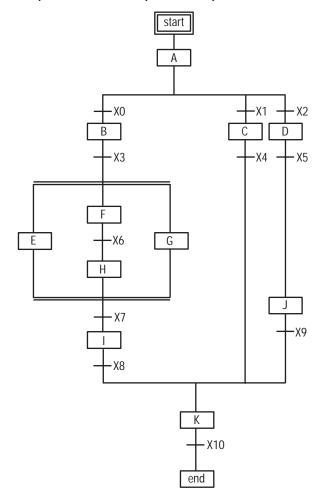

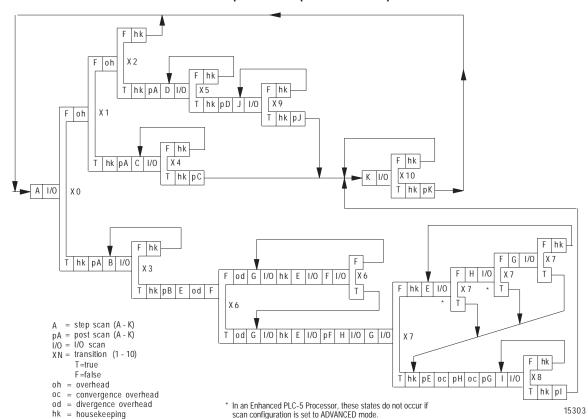

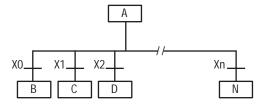

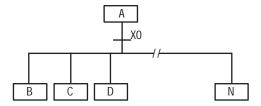

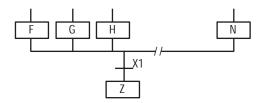

| SFC Reference                                | Appendix B-1Appendix ObjectivesB-1SFC Status Information in the Processor Status FileB-1Memory AllocationB-3Dynamic Constraints – Classic PLC-5 Processors OnlyB-5Scanning SequencesB-7Step and Transition ScanningB-7Selected Branch ScanningB-8Simultaneous Branch ScanningB-9SFC Example and Scan SequenceB-11Run Times – Classic PLC-5 ProcessorsB-12Using Sequence Diagrams to Determine Run TimeB-13Using Equations to Determine Run TimeB-14 |  |

| Valid Data Types for<br>Instruction Operands | Appendix C-1 Appendix Objectives                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

## Relay-Type Instructions XIC, XIO, OTE, OTL, OTU, IIN, IOT, IDI, IDO

#### **Using Relay-Type Instructions**

Use relay-type instructions to monitor and control the status of bits in the data table, such as input bits or timer control-word bits. The relay instructions let you:

| If You Want to:                                                                                                                  | Use this Instruction: | Found on Page: |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|

| Examine a bit for an ON condition                                                                                                | XIC                   | 1-3            |

| Examine a bit for an OFF condition                                                                                               | XIO                   | 1-3            |

| Hold a bit ON or OFF (non-retentive)                                                                                             | OTE                   | 1-4            |

| Latch a bit to ON (retentive)                                                                                                    | OTL                   | 1-4            |

| Unlatch a bit to OFF (retentive)                                                                                                 | ОТИ                   | 1-5            |

| Immediately update input image bits                                                                                              | IIN                   | 1-6            |

| Immediately update outputs                                                                                                       | IOT                   | 1-7            |

| Immediately perform an update of the ControlNet™ data input file from the ControlNet memory buffers.                             | IDI                   | 1-8            |

| Immediately perform an update of<br>the ControlNet memory buffers from<br>the source file before the next<br>output-image update | IDO                   | 1-8            |

With these instructions, you can address bits in all sections of data storage, but the examples in this chapter only show how to address bits in the I/O image files.

For more information on the operands (and valid data types/values of each operand) used by the instructions discussed in this chapter, see Appendix C.

If you use relay-type instruction (OTE, OTL, or OTU) with indirect addresses to set or reset a bit in the control file of a block-transfer or message instruction, there may be conflicting results. Even though the bit instruction is executed to set or reset a bit, its result might be overwritten by the block-transfer or message operation that sets or resets the same bit. These are asynchronous operations. The last operation to set or reset the bit is the value that is saved in the data table.

#### I/O Image Files in Data Storage

The input image file in the processor stores the status of input sensors connected to input module terminals.

| _ | If the Input Sensor Is: | Then Its Corresponding Input Image Bit Is: |

|---|-------------------------|--------------------------------------------|

| - | closed (on)             | on (1)                                     |

| • | open (off)              | off (0)                                    |

You program instructions in ladder logic to monitor bits. Use a logical address for the bit.

The output image file controls the status of actuators wired to output module terminals.

| If the Output Image Bit Is: | Then Its Corresponding Output Is: |

|-----------------------------|-----------------------------------|

| on (1)                      | energized (on)                    |

| off (0)                     | de-energized (off)                |

You program instructions in ladder logic to control bits.

#### **Rung Logic**

As each conditioning instruction is executed, the addressed bit is examined to see if it matches a certain condition (on or off). If a complete path of true conditions examined for are found, the rung is set to true. The rung must contain a continuous path of true instructions from the start of the rung to the output for the output to be enabled.

#### Examine On (XIC)

#### **Description:**

۸7

If you find an ON condition at bit I:012/07 in the input table, set this instruction true. This bit corresponds to input terminal 7 of a module in I/O group 2 of I/O rack 1. If the input circuit is true, the instruction is true.

When a device closes its circuit, the module whose input terminal is wired to the device detects the closed circuit. The processor reflects this ON state in the data table. When the processor finds an XIC instruction that addresses the bit that corresponds to the input terminal, the processor determines whether the device is ON (closed). If the processor finds an ON state, it sets the logic for this instruction true; if the processor finds an OFF state, it sets the logic for the instruction not true.

If the XIC instruction is the only conditioning instruction on the rung, the processor enables the output instruction when the XIC instruction is true (input closed). The processor disables an output instruction when the XIC instruction is false (input open).

The examine-on instruction is true or false depending on whether the processor finds an ON or OFF condition at the addressed bit.

| If the Bit Is: | Then the Instruction Is: | Bit Logic State: |

|----------------|--------------------------|------------------|

| on             | true                     | 1                |

| off            | false                    | 0                |

#### Examine Off (XIO)

#### **Description:**

Example:

If you find an OFF condition at bit I:012/07 in the input table, set this instruction true. This bit corresponds to input terminal 7 of a module in I/O group 2 of I/O rack 1. If the input circuit is false, the instruction is true.

When a device opens its circuit, the module whose input terminal is wired to the device detects an open circuit. The processor reflects this OFF state in the data table. When the processor finds an XIO instruction that addresses the bit that corresponds to the input terminal, the processor determines whether the device is OFF (open). If the processor finds an OFF state, it sets the logic for this instruction true. If the processor finds an ON state, it sets the XIO instruction to false.

If the XIO instruction is the only conditioning instruction on the rung, the processor enables the output instruction when the XIO instruction is true (input open).

The examine off instruction is true or false depending on whether the processor finds an OFF or ON condition at the addressed bit.

| If the Bit Is: | Then the Instruction Is: | Bit Logic State: |

|----------------|--------------------------|------------------|

| off            | true                     | 0                |

| on             | false                    | 1                |

#### **Energize (OTE)**

#### **Description:**

Example:

Turn ON bit 0:013/01 of the output image table if the rung is true. Turn it OFF if the rung is false. This bit corresponds to output terminal 01 of a module in /0 group 3 of I/O rack 1. Use the OTE instruction to control a bit in memory. If the bit corresponds to an output module terminal, the device wired to this terminal is energized when the instruction is enabled and de-energized when the instruction is disabled. If the input conditions that precede the OTE instruction are true, the processor enables the OTE instruction. If the input conditions that precede the OTE instruction are false, the processor disables the OTE instruction. When rung conditions become false, the corresponding device de-energizes.

An OTE instruction is similar to a relay coil. The OTE instruction is controlled by preceding input instructions; the relay coil is controlled by contacts in its hard-wired rung.

The OTE instruction tells the processor to control the addressed bit based on the rung condition:

| If the Rung Is: | Then the Processor Turns the Bit: | Bit Logic State: |

|-----------------|-----------------------------------|------------------|

| true            | on                                | 1                |

| false           | off                               | 0                |

#### Latch (OTL)

#### **Description:**

Example:

Turn ON bit 0:013/01 of the output image table if the rung is true.

This bit corresponds to output terminal 1 of a module in I/O group 3 of I/O rack 1.

The OTL instruction is a retentive output instruction that can only turn on a bit (it cannot turn off a bit). This instruction is usually used in pairs with an OTU (unlatch) instruction, with both instructions addressing the same bit.

When you assign an address to an OTL instruction that corresponds to a terminal of an output module, the output device wired to this terminal is energized when the processor sets (enables) the bit in processor memory. If the input conditions that precede the OTL instruction are true, the processor enables the OTL instruction. When rung conditions become false (after being true), the bit remains set and the corresponding output device remains energized. Use the OTU instruction to turn OFF the bit you latched on with the OTL instruction.

When enabled, the latch instruction tells the processor to turn on the addressed bit. Thereafter, the bit remains on, regardless of the rung condition, until the bit is turned off, typically by an unlatch (OTU) instruction in another rung.

If the Rung Is: Then the Processor Turns the Bit:

| true  | on        |

|-------|-----------|

| false | no change |

When the processor changes from Run to Program mode or when the processor loses power (and there is battery backup), the last true OTL instruction continues to control the bit in memory. The latched output device is energized even though the rung conditions that control the instruction may have gone false.

**Important:** The OTL instruction is retentive. When the processor loses power, is switched to Program mode or Test mode, or detects a major fault, outputs go off; but the states of retentive outputs are retained in memory. When the processor resumes operation in Run mode, retentive outputs immediately return to their previous states. Non-retentive outputs, such as OTE outputs, are reset.

#### Unlatch (OTU)

#### **Description:**

#### Example:

Turn OFF bit 0:013/01 of the output image table if the rung is true.

This bit corresponds to output terminal 1 of a module in I/O group 3 in I/O rack 1.

The OTU instruction is a retentive output instruction that can only turn off a bit (it cannot turn on a bit). This instruction is usually used in pairs with an OTL (output latch) instruction, with both instructions addressing the same bit. The OTU instruction turns OFF the bit, which was turned ON (latched) by the OTL instruction.

When the processor changes from Run to Program mode or when the processor loses power (and there is battery backup), the bit is retained in the state set by the last rung of the latch/unlatch pair that was true.

The unlatch instruction tells the processor to turn off the addressed bit based on the rung condition. Thereafter, the bit remains off, regardless of the rung condition, until it is turned on, typically by a OTL instruction in another rung.

If the Rung is: Then the Processor Turns the Bit:

| true  | off       |

|-------|-----------|

| false | no change |

#### Immediate Input (IIN)

#### **Description:**

#### Example:

RR = I/O rack number 00-03 PLC-5/10, -5/11, -5/12, -5/15, -5/20 00-07 PLC-5/25, -5/30 000-177 PLC-5/40, -5/40L 000-277 PLC-5/60, -5/60L, -5/80 G = I/O group number (0 - 7)

When the input conditions are true, update the input image word corresponding to I/O rack 0, group 1.

The IIN instruction is an output instruction that, when enabled, updates a word of input-image bits before the next regular input-image update.

For inputs in the local chassis, the program scan is interrupted while the inputs of the addressed I/O group are examined. This sets the input-image bits to the current states of the inputs before the program scan continues. If the program reaches an enabled IIN instruction while a block-transfer with the local chassis is in progress, the processor completes the block-transfer before executing the IIN instruction.

For inputs in a **remote chassis**, the program scan is interrupted only to update the input image with the latest states of the inputs as found in the remote I/O buffer (from the most recent remote I/O scan). The inputs are not scanned before the program scan continues.

Place the rung with the IIN instruction immediately before rungs that examine critical input bits updated by the IIN instruction.

For the IIN instruction, you only need to enter the I/O rack number and the I/O group number; you do not enter a file number.

ATTENTION: Do not enter an address that includes a file number, such as I:027. The processor interprets the bit pattern found at that address as the I/O rack and I/O group number of the inputs to update. Unexpected operation will result with possible damage to equipment and injury to personnel.

For more information on I/O scanning and block-transfers, see chapter 15.

#### **Immediate Output (IOT)**

#### **Description:**

When the input conditions are true, update the output image word corresponding to I/O rack 0, group 1.

The IOT instruction is an output instruction that, when enabled, updates an I/O group of outputs before the next normal outputimage update.

For outputs in the **local chassis**, the program scan is interrupted while the outputs of the addressed I/O group are examined. This sets the output circuits to the current states of the output bits in the output image table before the program scan continues. If the program reaches an enabled IOT instruction while a block-transfer is in progress, the processor completes the block-transfer before executing the IOT instruction.

For outputs in a **remote chassis**, the program scan is interrupted only to update the remote I/O buffer with the current states of the output-image bits. This makes these states immediately available for the next remote I/O scan while the program scan continues. The outputs are not scanned before the program scan continues.

Place the rung with the IOT output instruction immediately after rungs that control critical output image bits to be updated by the IOT instruction.

For the IOT instruction, you only need to enter the I/O rack number and the I/O group number; you do not need to enter the file number.

**ATTENTION:** Do not enter an address that includes a file number, such as O:027. The processor interprets the bit pattern found at that address as the I/O rack and I/O group number of the outputs to be updated. Unexpected operation will result with possible damage to equipment and injury to personnel.

For more information on I/O scanning and block-transfers, see chapter 15.

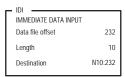

#### Immediate Data Input (IDI)

#### **Description:**

When the rung goes true, the IDI instruction performs an immediate update of the ControlNet data input file from the ControlNet memory buffers before the next normal input-image update (which occurs at the end of the program scan).

To program an IDI instruction, you must provide the processor with the following information that it stores in its control block:

- **Data file offset** specifies the offset into the Data Input File (DIF) where words are read can be an immediate value (0-999) or a logical address that specifies the data image file offset.

- **Length** specifies the number of words to be transferred an immediate value (0-64) or a logical address that specifies the number of words to be transferred.

- **Destination** specifies a data table address to be used as the destination of the words to be transferred.

**Important:** The Destination should be the matching data-table address in the Data Input File (DIF) except when you use the instruction to ensure data-block integrity in the case of Selectable Timed Interrupts (STIs). For more information, see page 1-9.

#### Immediate Data Output (IDO)

#### **Description:**

When the rung goes true, the IDO instruction performs an immediate update of the ControlNet memory buffers from the source file before the next output-image update, sending the updated data output file information across the ControlNet network to the appropriate ControlNet device.

To program an IDO instruction, you must provide the processor with the following information that it stores in its control block:

- Data file offset specifies the offset into the Data Output File (DOF) where words are written can be an immediate value (0-999) or a logical address that specifies the data image file offset.

- **Length** specifies the number of words to be transferred an immediate value (0-64) or a logical address that specifies the number of words to be transferred.

- Source specifies a data table address to be used as the source of the words to be transferred.

Important: The Source should be the matching data-table address in the Data Output File (DOF) except when you use the instruction to ensure data-block integrity in the case of Selectable Timed Interrupts (STIs). For more information, see page 1-9 www.nicsanat.com

021-87700210

#### **Using IDI and IDO Instructions**

You can use the IDI and IDO instructions for immediate data input and output on ControlNet.

For more detailed information about writing ladder programs, see your programming manual.

**Important:** Be careful when using Selectable Timed Interrupts (STIs) with a program on a ControlNet network.

A Selectable Timed Interrupt (STI) periodically interrupts primary program execution in order to run a subprogram to completion. If an STI occurs while a normal ControlNet non-discrete I/O transfer or a ControlNet Immediate Data I/O instruction (IDI or IDO) is in progress and they both operate on the same set of data, the integrity of that block of data is jeopardized.

To ensure data-block integrity, write your STI routine so that it operates on its own copy of the data block that it needs. Use ControlNet Immediate Data I/O instructions (IDI and IDO) within your STI to copy the needed block of data out to and back from a temporary location that is different from that used by the normal data table.

For detailed information on STIs, see your software user manual.

| Relay-Type Instructions XIC, XIO, OTE, OTL, OTU, IIN, IOT, IDI, IE |            |              |      |     |     |     |      |     |     |     |     |

|--------------------------------------------------------------------|------------|--------------|------|-----|-----|-----|------|-----|-----|-----|-----|

|                                                                    | Relay-Type | Instructions | XIC. | XIO | OTF | OTI | OTII | IIN | IOT | IDI | IDO |

# Timer Instructions TON, TOF, RTO Counter Instructions CTU, CTD Reset RES

#### **Using Timers and Counters**

Timers and counters let you control operations based on time or number of events. Table 2.A lists the available timer and counter instructions.

Table 2.A

Available Timer and Counter Instructions

| If You Want to:                                | Use this Instruction: | Found on Page: |

|------------------------------------------------|-----------------------|----------------|

| Delay turning on an output                     | TON                   | 2-4            |

| Delay turning off an output                    | TOF                   | 2-7            |

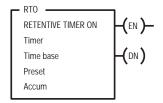

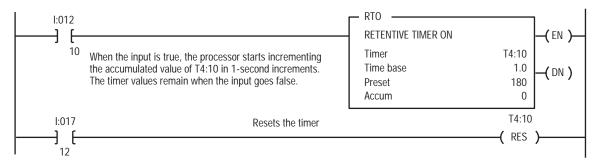

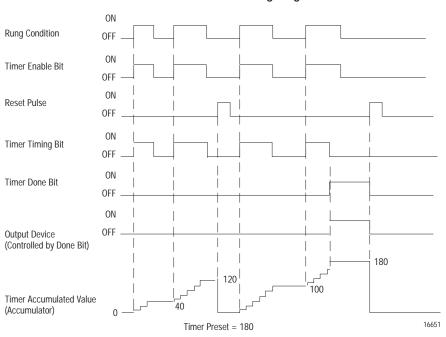

| Time an event retentively                      | RTO                   | 2-10           |

| Count up                                       | СТИ                   | 2-15           |

| Count down                                     | CTD                   | 2-17           |

| Reset a counter, timer, or counter instruction | RE                    | 2-20           |

For more information on the operands (and valid data types/values of each operand) used by the instructions discussed in this chapter, see Appendix C.

#### **Using Timers**

Before you program timer instructions, you need to understand the parameters that you enter for timer instructions and how timer accuracy works.

#### **Entering Parameters**

To program a timer instruction, provide the processor with the following information:

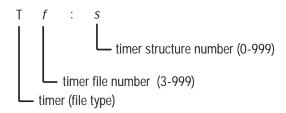

• **Timer** is the timer control address in the timer (T) area of data storage. Use the following address format:

Important: You can use any timer file number from 3 to 999; however, the default timer file number is 4. If you want to specify a timer file number as any file between 3 and 8 (other than the default 4), you must first delete the entire default file for that number, and then create the timer file. For example, if you want a timer file number as file 3, you must first delete the entire default binary file and then create the timer file as file 3.

To access a timer status bit, preset, or accumulated value stored at the timer control address, use the following address format:

| Status Bit | Preset            | Accumulated Value |

|------------|-------------------|-------------------|

| Tf:s.sb    | T <i>f:s.</i> PRE | Tf:s.ACC          |

The sb specifies a status bit mnemonic, such as .DN

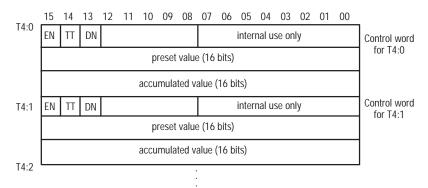

**Important:** The processor stores timer status bits and the preset and accumulated values in a 48-bit storage structure (three 16-bit words) in a timer file (T).

• **Time Base** determines how the timer operates. Table 2.B lists the possible time bases.

Table 1.B Available Time Base Values

| Enter This Time Base: | The Accumulated Value Range Is:                |

|-----------------------|------------------------------------------------|

| 1 second              | to 32,767 time-base intervals (to 9.1hours)    |

| 0.01 seconds (10ms)   | to 32,767 time-base intervals (to 5.5 minutes) |

• **Preset** specifies the value which the timer must reach before the processor sets the done bit (.DN). You must enter a preset value from 0-32,767. The processor stores the preset value as a 16-bit integer value.

**Important:** The Preset value operates differently if you are using a TOF instruction. See page 2-7 for more information.

• Accumulated Value is the number of time increments the instruction has counted. When enabled, the timer updates this value continually. Typically, enter zero when programming the instruction. If you enter a value, the instruction starts counting time base intervals from that value. If the timer is reset, the accumulated value is zero. The range for the accumulated value is 0-32,767. The processor stores the accumulated value as a 16-bit integer.

**Important:** The Accumulated value operates differently if you are using a TOF instruction. See page 2-7 for more information.

Timer accuracy refers to the length of time between the moment the processor enables a timer instruction and the moment the processor completes the timed interval. Timer accuracy depends on the processor clock tolerance and the time base. The clock tolerance is  $\pm 0.02\%$ . This means that a timer could time out early or late by 0.01 seconds (10ms) for a 0.01 second time base or 1 second for a 1 second time base.

The 0.01-second timer maintains accuracy with a program scan of up to 2.5 seconds; the 1-second timer maintains accuracy with a program scan of up to 1.5 seconds. If your programs can exceed 1.5 or 2.5 seconds, repeat the timer instruction rung so that the rung is scanned within these limits.

The displayed accumulated value of a timer shows actual time but is dependent on CRT update time. The accumulated value might appear to be less than the preset when the done bit is set.

#### **Timer Accuracy**

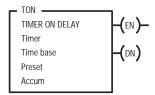

#### Timer On Delay (TON)

#### **Description:**

Use the TON instruction to turn an output on or off after the timer has been on for a preset time interval. The TON instruction starts accumulating time when the rung goes true, and continues until one of the following happens:

- the accumulated value equals its preset value

- the rung goes false

- a reset instruction resets the timer

- the SFC step goes inactive

- the processor resets the accumulated value when the rung conditions go false, regardless of whether the timer timed out or not

#### **Using Status Bits**

Examine status bits in the ladder program to trigger some event. The processor changes the states of status bits when the processor runs this instruction. You address status bits by mnemonic.

| This Bit:                     | Is Set When:                                       | Indicates:                             | And Remains Set Until One of the Following Occurs:                                                                                                                             |

|-------------------------------|----------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer Enable.EN (bit 15)      | the rung goes true                                 | that the timer is enabled              | <ul><li> the rung goes false</li><li> a reset instruction resets the timer</li><li> the SFC step goes inactive</li></ul>                                                       |

| Timer Timing Bit .TT (bit 14) | the rung goes true                                 | that a timing operation is in progress | <ul> <li>the rung goes false</li> <li>the .DN bit is set (.ACC = .PRE)</li> <li>a reset instruction resets the timer</li> <li>the associated SFC step goes inactive</li> </ul> |

| Timer Done Bit .DN (bit 13)   | the accumulated value is equal to the preset value | that a timing operation is complete    | <ul><li> the rung goes false</li><li> a reset instruction resets the timer</li><li> the associated SFC step goes inactive</li></ul>                                            |

If you set the done bit .DN using an OTE instruction, for example, you can pause the timer. The .EN and .TT bits remain set, but the accumulated value does not increment. Timing resumes when you clear the .DN bit. If the rung goes false while the timer is paused, the timer resets as normal.

- 1. If you change to Program mode, or the processor loses power before the instruction reaches the preset value, the following occurs:

- timer enable (.EN) bit remains set

- timer timing (.TT) bit remains set

- accumulated (.ACC) value remains the same

- **2.** Then when you switch back to Run mode or Test mode or power is restored, the following happens:

| Condition:            | Result:                                                                                                           |

|-----------------------|-------------------------------------------------------------------------------------------------------------------|

| If the rung is true:  | .EN bit remains set<br>.TT bit remains set<br>.DN bit remains reset<br>.ACC value is reset and starts counting up |

| If the rung is false: | .EN bit is reset<br>.TT bit is reset<br>.DN bit is reset<br>.ACC value is reset                                   |

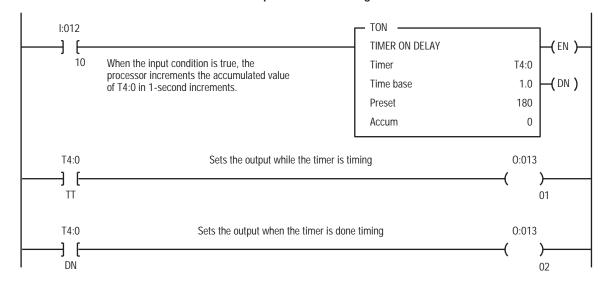

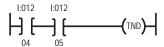

Figure 2.1 Example TON Ladder Diagram

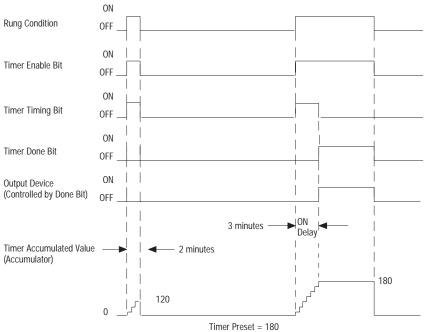

When bit I:012/10 is set, the processor starts T4:0. The accumulated value increments in 1-second intervals. T4:0.TT is set and output bit 0:013/01 is set (the associated output device is energized) while the timer is timing. When the timer is finished (.ACC = .PRE) T4:0.TT is reset (so 0:013/01 and the associated output device is de-energized) and T4:0.DN is set (so 0:013/02 is set and the associated output device is energized). When the accumulated value reaches 180, the .DN bit is set. Or if the rung goes false, the timer is reset.

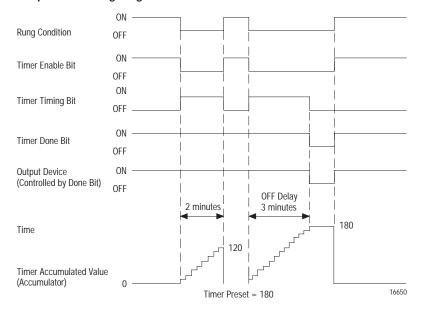

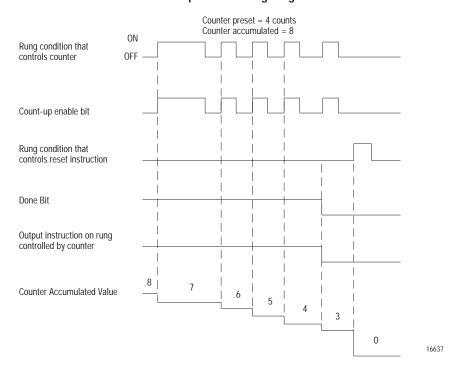

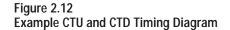

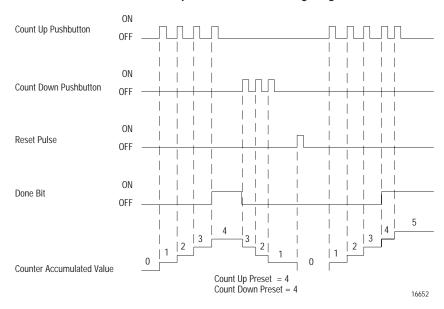

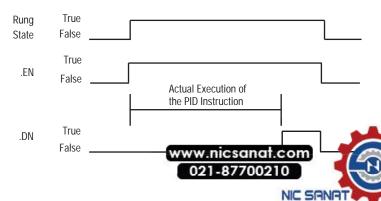

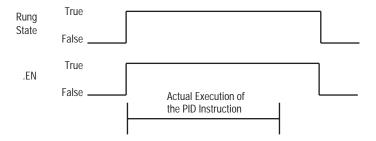

Figure 2.2 Example TON Timing Diagram

16649

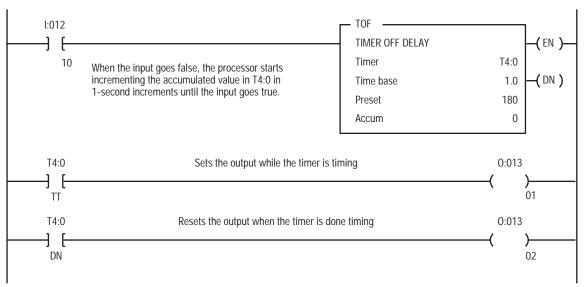

#### Timer Off Delay (TOF)

#### **Description:**

Use the TOF instruction to turn an output on or off after its rung has been off for a preset time interval. The TOF instruction starts accumulating time when the rung goes false and continues timing until one of the following conditions occur:

- the accumulated value equals its preset value

- the rung goes true

- a reset instruction resets the timer

- the SFC step goes inactive

The processor resets the accumulated value when the rung conditions go true, regardless of whether the timer timed out or not.

#### **Using Status Bits**

Examine status bits in the ladder program to trigger some event. The processor changes the states of status bits when the processor runs this instruction. You address the status bits by mnemonic.

| This Bit:                     | Is Set When:                                                                | And Remains Set Until One of the Following Occurs:                                                                                                                            |

|-------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer Enable .EN (bit 15)     | the rung goes true                                                          | <ul><li> the rung goes false</li><li> a reset instruction resets the timer</li><li> the SFC step goes inactive</li></ul>                                                      |

| Timer Timing Bit .TT (bit 14) | the rung goes false and the<br>accumulated value is less than<br>the preset | <ul> <li>the rung goes true</li> <li>the .DN bit is set (.ACC = .PRE)</li> <li>a reset instruction resets the timer</li> <li>the associated SFC step goes inactive</li> </ul> |

| Timer Done Bit .DN (bit 13)   | the rung goes true                                                          | the accumulated value is equal to the preset value                                                                                                                            |

If you set the done bit .DN using an OTE instruction, for example, you can pause the timer. The .EN and .TT bits remain set, but the accumulated value does not increment. Timing resumes when you clear the .DN bit. If the rung goes false while the timer is paused, the timer resets as normal.

- 1. If you change to Program mode, or the processor loses power, or the processor fault interrupts the TOF instruction before it reaches the preset value, the following occurs:

- timer enable (.EN) bit remains reset

- timer timing (.TT) bit remains set

- timer done (.DN) bit remains set

- accumulated (.ACC) value remains the same

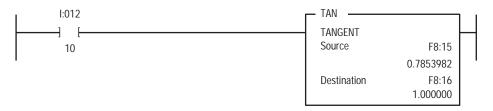

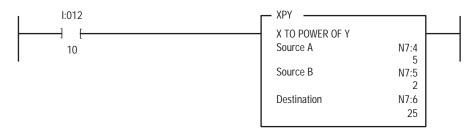

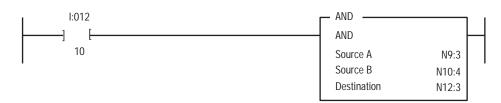

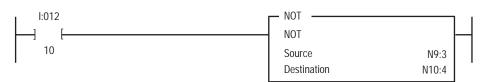

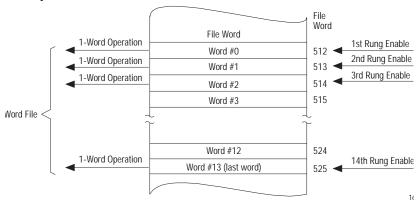

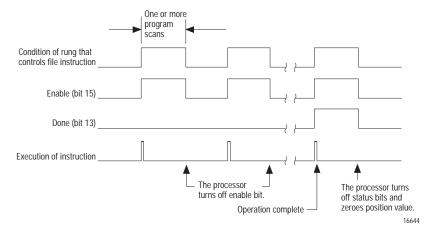

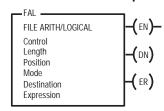

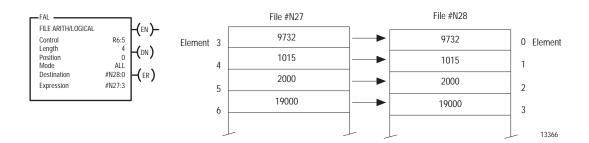

- **2.** Then if you switch to Run mode or Test mode, the following happens: