# **FX Series Programmable Controllers**

## **Programming Manual**

Manual number: JY992D48301

Manual revision: J

Date: November 1999

#### **Foreword**

- This manual contains text, diagrams and explanations which will guide the reader in the correct programming and operation of the PLC.

- Before attempting to install or use the PLC this manual should be read and understood.

- If in doubt at any stage of the installation of the PLC always consult a professional electrical engineer who is qualified and trained to the local and national standards which apply to the installation site.

- If in doubt about the operation or use of the PLC please consult the nearest Mitsubishi Electric distributor.

- · This manual is subject to change without notice.

#### **FAX BACK - Combined Programming Manual (J)**

Mitsubishi has a world wide reputation for its efforts in continually developing and pushing back the frontiers of industrial automation. What is sometimes overlooked by the user is the care and attention to detail that is taken with the documentation. However,to continue this process of improvement, the comments of the Mitsubishi users are always welcomed. This page has been designed for you,the reader,to fill in your comments and fax them back to us. We look forward to hearing from you.

Please tick the box of your choice;

| Fax numbers:                                                                                                                        |                                                                | Your na      | ame                 |                    |  |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------|---------------------|--------------------|--|

| Mitsubishi Electric                                                                                                                 |                                                                |              |                     |                    |  |

| America                                                                                                                             | (01) 847-478-2253                                              | Your co      | Your company        |                    |  |

| Australia                                                                                                                           | (02) 638-7072                                                  |              |                     |                    |  |

| Germany                                                                                                                             | (0 21 02) 4 86-1 12                                            | Your lo      | cation:             |                    |  |

| South Africa                                                                                                                        | (0111) 444-8304                                                |              |                     |                    |  |

| United Kingdom                                                                                                                      | (01707) 278-695                                                |              |                     |                    |  |

| What condition did                                                                                                                  | the manual arrive in?                                          | □Good        | □Minor damage       | □Unusable          |  |

| Will you be using a                                                                                                                 | folder to store the manual                                     | l?           | □Yes                | □No                |  |

| What do you think t                                                                                                                 | to the manual presentation                                     | 1?           | □Tidy               | □Un-friendly       |  |

| Are the explanation                                                                                                                 | ns understandable?                                             | □Yes         | □Not too bad        | □Unusable          |  |

| •                                                                                                                                   | was most difficult to under                                    |              |                     |                    |  |

|                                                                                                                                     | ams which are not clear?                                       |              | □Yes                | □No                |  |

| If so,which:                                                                                                                        |                                                                |              |                     |                    |  |

| What do you think to the manual layout? □G                                                                                          |                                                                | □Good        | □Not too bad        | □Un-helpful        |  |

|                                                                                                                                     | If there one thing you would like to see improved, what is it? |              |                     |                    |  |

| Could you find the information you required easily using the index and/or the contents,if possible please identify your experience: |                                                                |              |                     |                    |  |

|                                                                                                                                     | omments in general about                                       |              |                     |                    |  |

| Thank you for takin and this manual ea                                                                                              | g the time to fill out this qu                                 | ıestionnaire | . We hope you found | I both the product |  |

# Guidelines for the Safety of the User and Protection of the Programmable Controller (PLC)

This manual provides information for the use of the FX family of PLC's. The manual has been written to be used by trained and competent personnel. The definition of such a person or persons is as follows;

- a) Any engineer who is responsible for the planning, design and construction of automatic equipment using the product associated with this manual should be of a competent nature, trained and qualified to the local and national standards required to fulfill that role. These engineers should be fully aware of all aspects of safety with regards to automated equipment.

- b) Any commissioning or service engineer must be of a competent nature, trained and qualified to the local and national standards required to fulfill that job. These engineers should also be trained in the use and maintenance of the completed product. This includes being completely familiar with all associated documentation for the said product. All maintenance should be carried out in accordance with established safety practices.

- c) All operators of the completed equipment should be trained to use that product in a safe and coordinated manner in compliance to established safety practices. The operators should also be familiar with documentation which is connected with the actual operation of the completed equipment.

**Note**: the term 'completed equipment' refers to a third party constructed device which contains or uses the product associated with this manual.

#### Note's on the Symbols used in this Manual

At various times through out this manual certain symbols will be used to highlight points of information which are intended to ensure the users personal safety and protect the integrity of equipment. Whenever any of the following symbols are encountered its associated note must be read and understood. Each of the symbols used will now be listed with a brief description of its meaning.

#### **Hardware Warnings**

1) Indicates that the identified danger **WILL** cause physical and property damage.

2) Indicates that the identified danger could **POSSIBLY** cause physical and property damage.

3) Indicates a point of further interest or further explanation.

#### **Software Warnings**

4) Indicates special care must be taken when using this element of software.

5) Indicates a special point which the user of the associate software element should be aware of.

6) Indicates a point of interest or further explanation.

#### **Contents**

| 1. Introduction                                      | 1-1  |

|------------------------------------------------------|------|

| 1.1 Overview                                         | 1-1  |

| 1.2 What is a Programmable Controller?               |      |

| 1.3 What do You Need to Program a PLC?               |      |

| 1.4 CPU version numbers                              |      |

| 1.4.1 FX0N CPU versions                              |      |

| 1.4.2 FX and FX2C CPU versions                       | 1-3  |

| 1.5 Special considerations for programming equipment | 1-4  |

| 1.5.1 FX CPU version 3.07 or later and FX2C          | 1-4  |

| 1.5.2 FX2N(C) CPU all versions                       | 1-5  |

| 2. Basic Program Instructions                        | 2-1  |

| 2.1 What is a Program?                               |      |

| 2.2 Outline of Basic Devices Used in Programming     |      |

| 2.3 How to Read Ladder Logic                         |      |

| 2.4 Load, Load Inverse                               |      |

| 2.5 Out                                              | 2-4  |

| 2.5.1 Timer and Counter Variations                   | 2-4  |

| 2.5.2 Double Coil Designation                        |      |

| 2.6 And, And Inverse                                 |      |

| 2.7 Or, Or Inverse                                   |      |

| 2.8 Load Pulse, Load Trailing Pulse                  |      |

| 2.9 And Pulse, And Trailing Pulse                    |      |

| 2.10 Or Pulse, Or Trailing Pulse                     |      |

| 2.11 Or Block                                        |      |

| 2.12 And Block                                       |      |

| 2.13 MPS, MRD and MPP                                |      |

| 2.14 Master Control and Reset                        |      |

| 2.15 Set and Reset                                   | 2-17 |

| 2.16 Timer, Counter (Out & Reset)                    |      |

| 2.16.1 Basic Timers, Retentive Timers And Counters   |      |

| 2.16.2 Normal 32 bit Counters                        |      |

| 2.16.3 High Speed Counters                           |      |

| 2.17 Leading and Trailing Pulse                      |      |

| 2.18 Inverse                                         |      |

| 2.19 No Operation                                    |      |

| 2.20 End                                             | 2-23 |

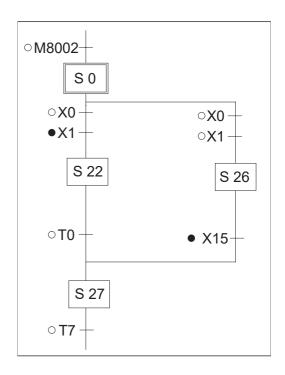

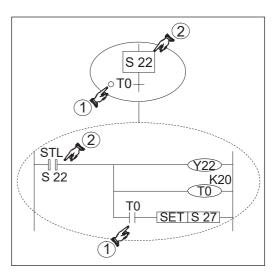

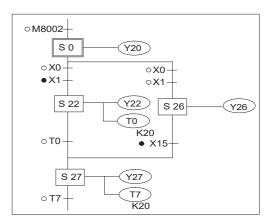

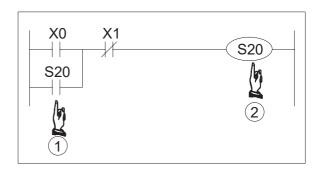

| 3. STL Programming                                            | 3-1  |

|---------------------------------------------------------------|------|

| 3.1 What is STL, SFC And IEC1131 Part 3?                      |      |

| 3.2 How STL Operates                                          |      |

| 3.2.1 Each step is a program                                  |      |

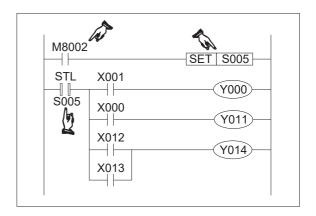

| 3.3 How To Start And End An STL Program                       |      |

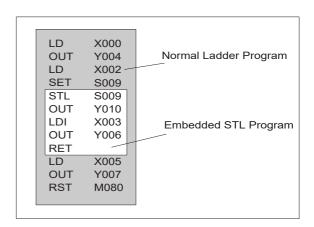

| 3.3.1 Embedded STL programs                                   | 3-3  |

| 3.3.2 Activating new states                                   |      |

| 3.3.3 Terminating an STL Program                              |      |

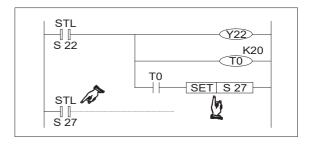

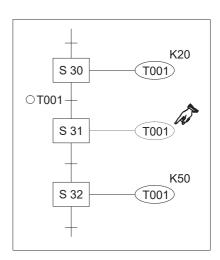

| 3.4 Moving Between STL Steps                                  |      |

| 3.4.1 Using SET to drive an STL coil                          |      |

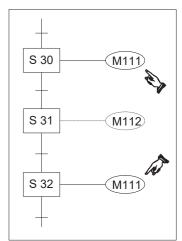

| 3.4.2 Using OUT to drive an STL coil                          |      |

| 3.5 Rules and Techniques For STL programs                     |      |

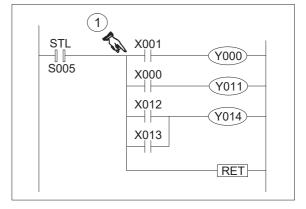

| 3.5.2 Single Signal Step Control                              |      |

| 3.6 Restrictions Of Some Instructions When Used With STL      |      |

| 3.7 Using STL To Select The Most Appropriate Program          |      |

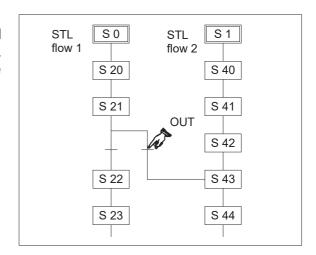

| 3.8 Using STL To Activate Multiple Flows Simultaneously       |      |

| 3.9 General Rules For Successful STL Branching                |      |

| 3.10 General Precautions When Using The FX-PCS/AT-EE Software |      |

| 3.11 Programming Examples                                     |      |

| 3.11.1 A Simple STL Flow                                      |      |

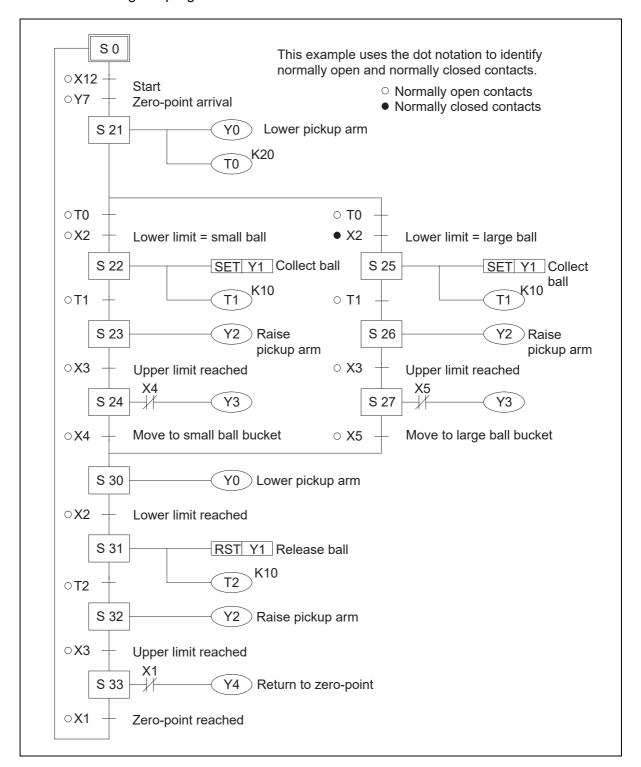

| 3.11.2 A Selective Branch/ First State Merge Example Program  | 3-18 |

| 3.12 Advanced STL Use                                         | 3-20 |

|                                                               |      |

| 4. Devices in Detail                                          | 4-1  |

| 4.1 Inputs                                                    |      |

| 4.2 Outputs                                                   |      |

| 4.3 Auxiliary Relays                                          |      |

| 4.3.1 General Stable State Auxiliary Relays                   |      |

| 4.3.2 Battery Backed/ Latched Auxiliary Relays                |      |

| 4.3.3 Special Diagnostic Auxiliary Relays                     |      |

| 4.3.4 Special Single Operation Pulse Relays                   |      |

| 4.4 State Relays                                              |      |

| 4.4.1 General Stable State - State Relays                     |      |

| 4.4.2 Battery Backed/ Latched State Relays                    |      |

| 4.4.3 STL Step Relays4.4.4 Annunciator Flags                  |      |

| 4.5 Pointers                                                  |      |

| 4.6 Interrupt Pointers                                        |      |

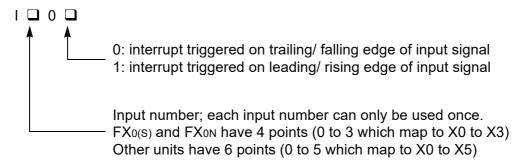

| 4.6.1 Input Interrupts                                        |      |

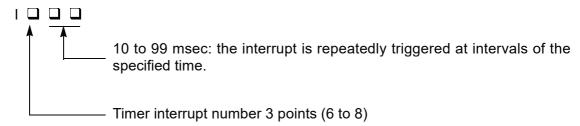

| 4.6.2 Timer Interrupts                                        |      |

| 4.6.3 Disabling Individual Interrupts                         |      |

| 4.6.4 Counter Interrupts                                      | 4-13 |

| 4.7 Constant K                                                |      |

| 4.8 Constant H                                                |      |

| 4.9 Timers                                                    |      |

| 4.9.1 General timer operation                                 |      |

| 4.9.2 Selectable Timers                                       |      |

| 4.9.3 Retentive Timers                                        |      |

| 4.9.4 Timers Used in Interrupt and 'CALL' Subroutines         |      |

| 4.9.5 Timer Accuracy                                          |      |

| 4.10 Counters                                                 |      |

| 4.10.1 General/ Latched 10bit OF Counters                     |      |

| 4. IV.Z GCIICIAI/ LAIGIICU JZDII DI UII CGIIOIIAI COUITICIS   |      |

www.nicsanat.com 021-87700210

| 4.11 High Speed Counters                                               | 4-22 |

|------------------------------------------------------------------------|------|

| 4.11.1 Basic High Speed Counter Operation                              | 4-23 |

| 4.11.2 Availability of High Speed Counters on FX0, FX0S and FX0N PLC's | 4-24 |

| 4.11.3 Availability of High Speed Counters on FX, FX2C PLC's           | 4-25 |

| 4.11.4 Availability of High Speed Counters on FX2N(C) PLC's            | 4-28 |

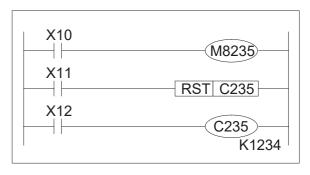

| 4.11.5 1 Phase Counters - User Start and Reset (C235 - C240)           | 4-29 |

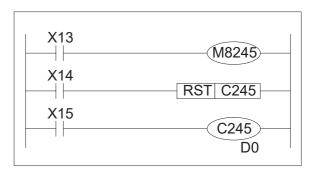

| 4.11.6 1 Phase Counters - Assigned Start and Reset (C241 to C245)      | 4-30 |

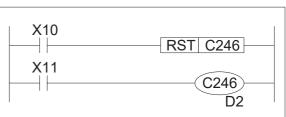

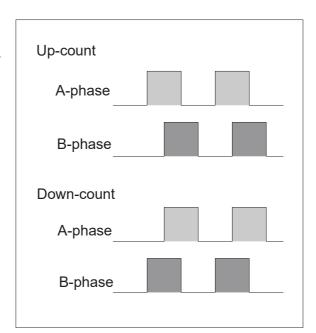

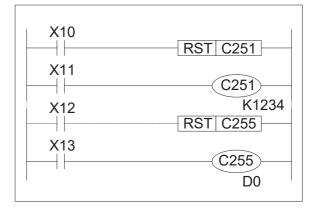

| 4.11.7 2 Phase Bi-directional Counters (C246 to C250)                  | 4-31 |

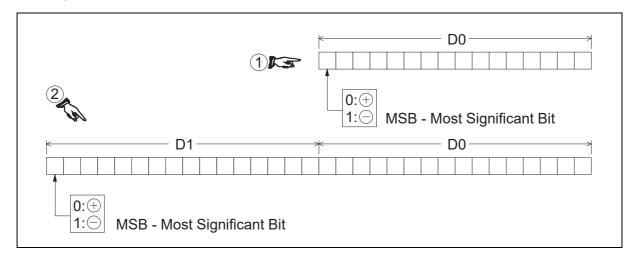

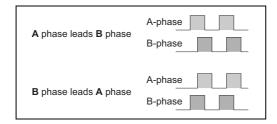

| 4.11.8 A/B Phase Counters (C252 to C255)                               | 4-32 |

| 4.12 Data Registers                                                    |      |

| 4.12.1 General Use Registers                                           | 4-34 |

| 4.12.2 Battery Backed/ Latched Registers                               | 4-35 |

| 4.12.3 Special Diagnostic Registers                                    | 4-35 |

| 4.12.4 File Registers                                                  | 4-36 |

| 4.12.5Externally Adjusted Registers                                    | 4-37 |

| 4.13 Index Registers                                                   | 4-38 |

| 4.13.1 Modifying a Constant                                            | 4-39 |

| 4.13.2 Misuse of the Modifiers                                         |      |

| 4.13.3 Using Multiple Index Registers                                  | 4-39 |

| 4.14 Bits, Words, BCD and Hexadecimal                                  | 4-40 |

| 4.14.1 Bit Devices, Individual and Grouped                             |      |

| 4.14.2 Word Devices                                                    |      |

| 4.14.3 Interpreting Word Data                                          | 4-42 |

| 4.14.4 Two's Compliment                                                |      |

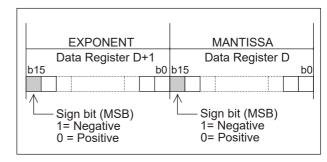

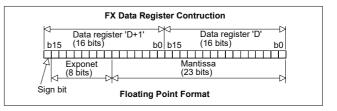

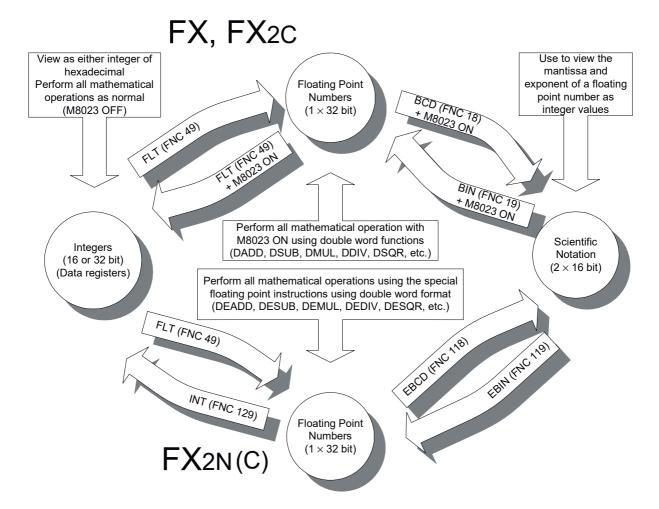

| 4.15 Floating Point And Scientific Notation                            |      |

| 4.15.1 Scientific Notation                                             |      |

| 4.15.2 Floating Point Format                                           |      |

| 4.15.3 Summary Of The Scientific Notation and Floating Point Numbers   |      |

|   |         | d Instructions                                    |      |

|---|---------|---------------------------------------------------|------|

| ļ | 5.1 Pro | gram Flow-Functions00 to 09                       | 5-4  |

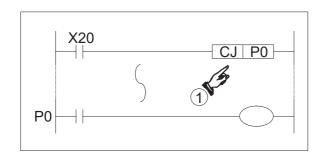

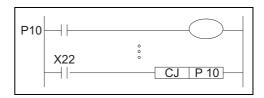

|   |         | CJ (FNC 00)                                       |      |

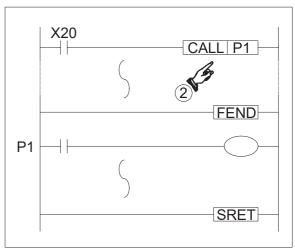

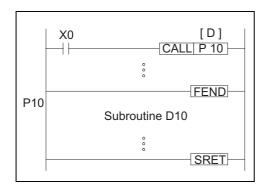

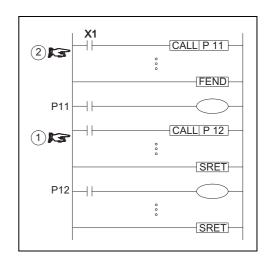

|   |         | CALL (FNC 01)                                     |      |

|   | 5.1.3   | SRET (FNC 02)                                     | 5-8  |

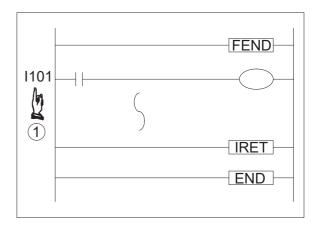

|   | 5.1.4   | IRET, ÈI, DI (FNC 03, 04, 05)                     | 5-9  |

|   | 5.1.5   | FEND (FNC 06)                                     | 5-11 |

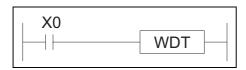

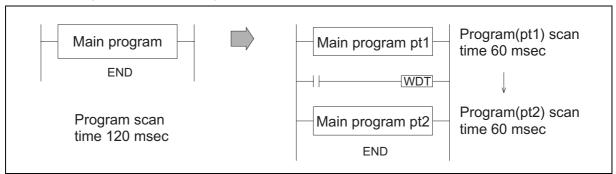

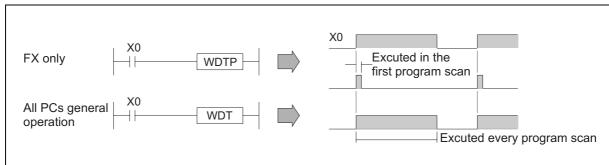

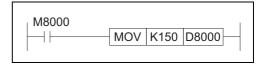

|   | 5.1.6   | WDT (FNC 07)                                      | 5-12 |

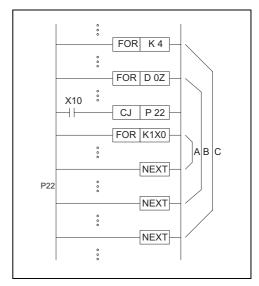

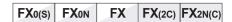

|   |         | FOR, NEXT (FNC 08, 09)                            |      |

| ļ | 5.2 Mo  | ve And Compare - Functions 10 to 19               | 5-16 |

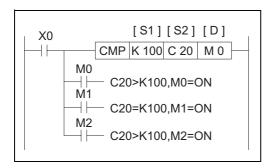

|   |         | CMP (FNC 10)                                      |      |

|   |         | ZCP (FNC 11)                                      |      |

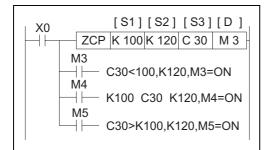

|   |         | MOV (FNC 12)                                      |      |

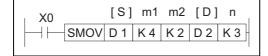

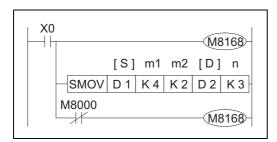

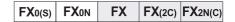

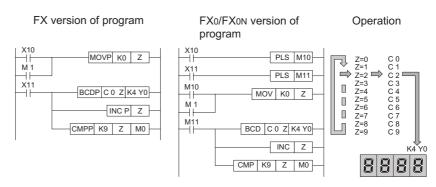

|   |         | SMOV (FNC 13)                                     |      |

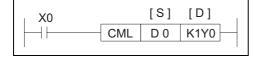

|   |         | CML (FNC 14)                                      |      |

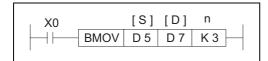

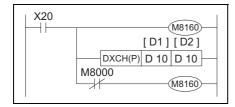

|   |         | BMOV (FNC 15)                                     |      |

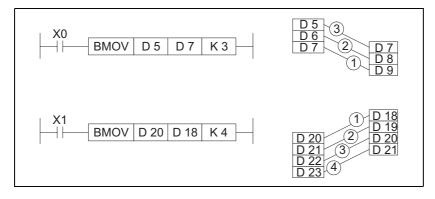

|   |         | FMOV (FNC 16)                                     |      |

|   |         | XCH (FNC 17)                                      |      |

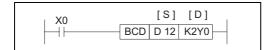

|   |         | BCD (FNC18)                                       |      |

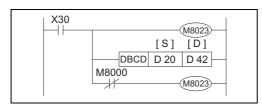

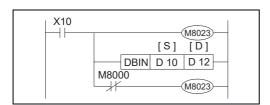

|   |         | BIN (FNC 19)                                      |      |

| ; |         | hmetic And Logical Operations -Functions 20 to 29 |      |

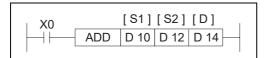

|   |         | ADD (FNC 20)                                      |      |

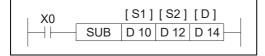

|   |         | SUB (FNC 21)                                      |      |

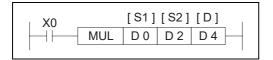

|   |         | MUL (FNC 22)                                      |      |

|   |         | DIV (FNC 23)                                      |      |

|   |         | INC (FNC 24)                                      |      |

|   |         | DEC (FNC 24)                                      |      |

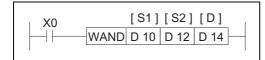

|   |         | WAND (FNC 26)                                     |      |

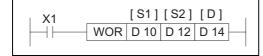

|   |         | WOR (FNC 27)                                      |      |

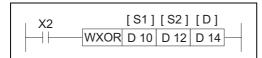

|   |         | WXOR (FNC 28)                                     |      |

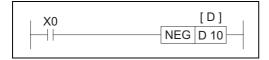

|   |         | NEG (FNC 29)                                      |      |

| ; |         | ration And Shift - Functions 30 to 39             |      |

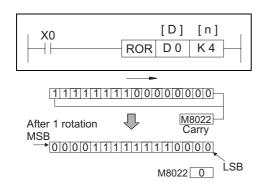

|   |         | ROR (FNC 30)                                      |      |

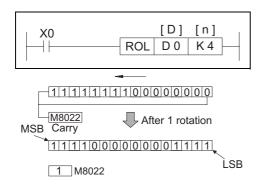

|   |         | ROL (FNC 31)                                      |      |

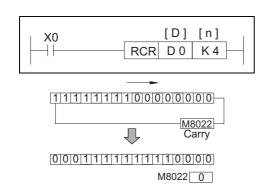

|   |         | RCR (FNC 32)                                      |      |

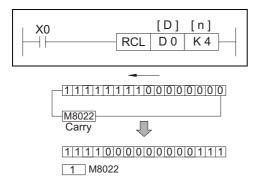

|   |         | RCL (FNC 33)                                      |      |

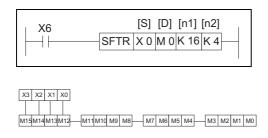

|   |         | SFTR (FNC 34)                                     |      |

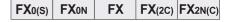

|   |         | SFTL (FNC 35)                                     |      |

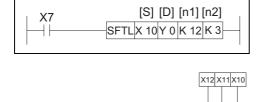

|   |         | WSFR (FNC 36)                                     |      |

|   |         | WSFL (FNC 37)                                     |      |

|   |         | SFWR (FNC 38)                                     |      |

|   |         | SFRD (FNC 39)                                     |      |

| ; |         | a Operation - Functions 40 to 49                  |      |

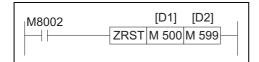

|   |         | ZRST (FNC 40)                                     |      |

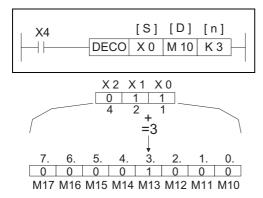

|   |         | DECO (FNC 41)                                     |      |

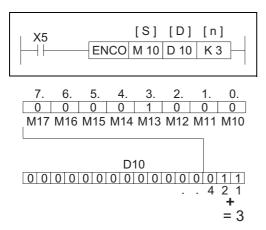

|   |         | ENCO (FNC 42)                                     |      |

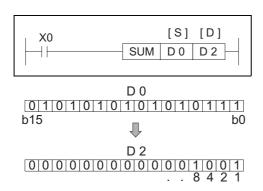

|   |         | SUM (FNC 44)                                      |      |

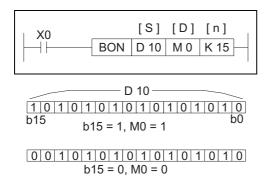

|   |         | BON (FNC 44)                                      |      |

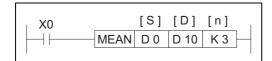

|   |         | MEAN (FNC 45)                                     |      |

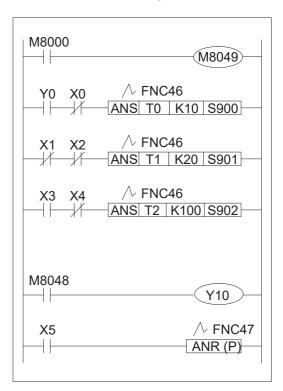

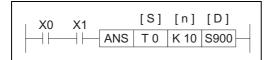

|   |         | ANS (FNC 46)                                      |      |

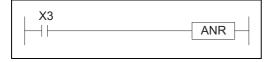

|   |         | ANR (FNC 47)                                      |      |

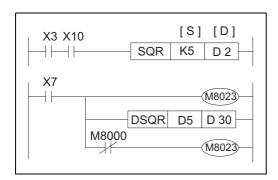

|   |         | SQR (FNC 48)                                      |      |

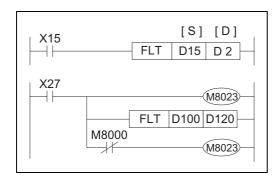

|   | 5.5.10  | FLT (FNC 49)                                      | 5-49 |

|          | h Speed Processing - Functions 50 to 59      |       |

|----------|----------------------------------------------|-------|

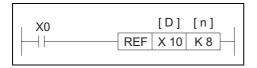

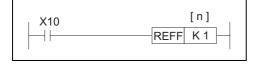

|          | REF (FNC 50)                                 |       |

| 5.6.2    | REFF (FNC 51)                                | 5-53  |

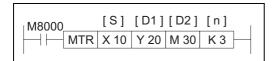

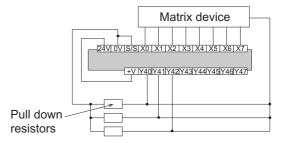

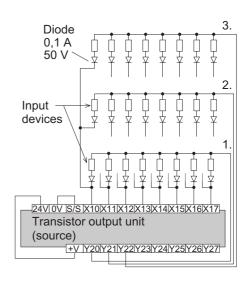

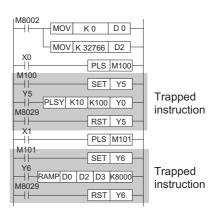

| 5.6.3    | MTR (FNC 52)                                 | 5-54  |

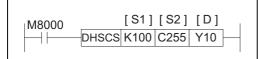

| 5.6.4    | HSCS (FNC 53)                                | 5-55  |

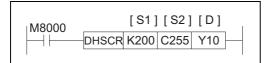

| 5.6.5    | HSCR (FNC 54)                                | 5-56  |

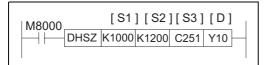

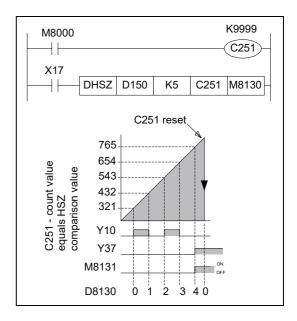

| 5.6.6    | HSZ (FNC 55)                                 | 5-57  |

| 5.6.7    | SPD (FNC 56)                                 | 5-60  |

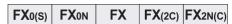

| 5.6.8    | PLSY (FNC 57)                                | 5-61  |

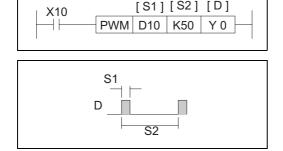

| 5.6.9    | PWM (FNC 58)                                 | 5-62  |

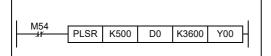

| 5.6.10   | PLSR (FNC 59)                                | 5-63  |

| 5.7 Ha   | ndy Instructions - Functions 60 to 69        | 5-66  |

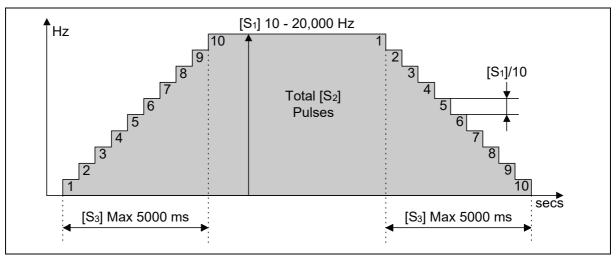

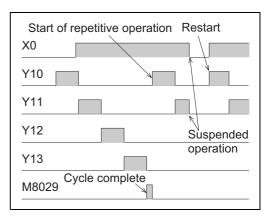

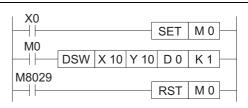

|          | IST (FNC 60)                                 |       |

|          | SER (FNC 61)                                 |       |

|          | ABSD (FNC 62)                                |       |

|          | INCD (FNC 63)                                |       |

|          | TTMR (FNC 64)                                |       |

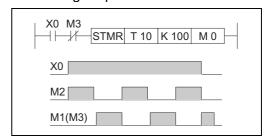

|          | STMR (FNC 65)                                |       |

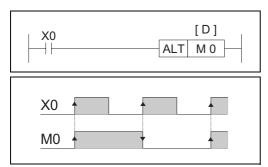

|          | ALT (FNC 66)                                 |       |

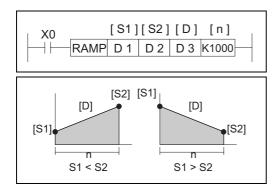

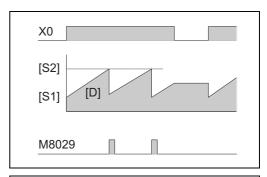

|          | RAMP (FNC 67)                                |       |

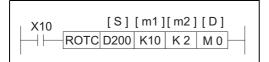

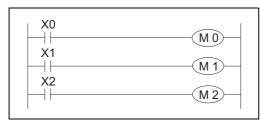

|          | ROTC (FNC 68)                                |       |

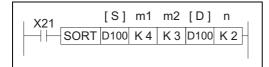

|          | SORT (FNC 69)                                |       |

|          | ernal FX I/O Devices - Functions 70 to 79    |       |

|          |                                              |       |

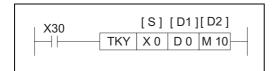

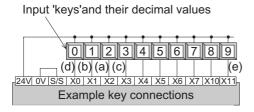

|          | TKY (FNC 71)                                 |       |

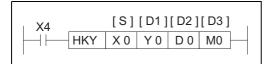

|          | HKY (FNC 71)                                 |       |

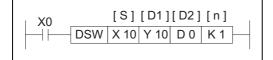

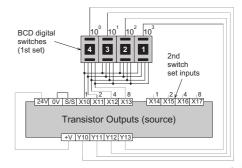

|          | DSW (FNC 72)                                 |       |

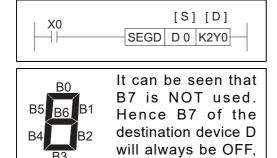

|          | SEGD (FNC 73)                                |       |

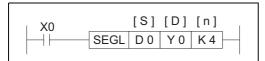

|          | SEGL (FNC 74)                                |       |

|          | ARWS (FNC 75)                                |       |

|          | ASC (FNC 76)                                 |       |

|          | PR (FNC 77)                                  |       |

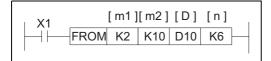

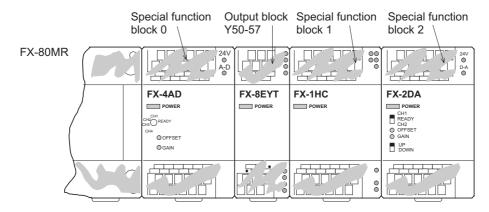

|          | FROM (FNC 78)                                |       |

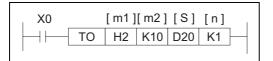

|          | TO (FNC 77)                                  |       |

|          | ernal FX Serial Devices - Functions 80 to 89 |       |

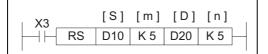

|          | RS (FNC 80)                                  |       |

|          | RUN (FNC 81)                                 |       |

|          | ASCI (FNC 82)                                |       |

|          | HEX (FNC 83)                                 |       |

|          | CCD (FNC 84)                                 |       |

|          | VRRD (FNC 85)                                |       |

| 5.9.7    | VRSD (FNC 86)                                | 5-102 |

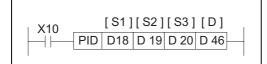

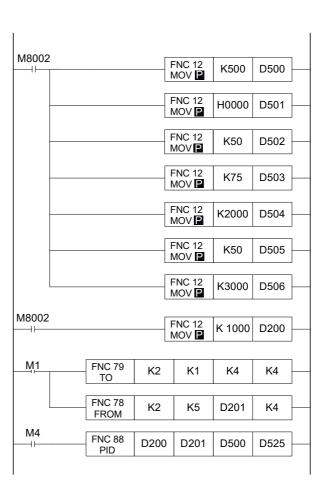

| 5.9.8    | PID (FNC 88)                                 | 5-103 |

| 5.10 Ext | ernal F2 Units - Functions 90 to 99          | 5-111 |

| 5.10.1   | MNET (FNC 90)                                | 5-112 |

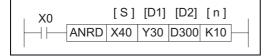

|          | ? ANRD (FNC 91)                              |       |

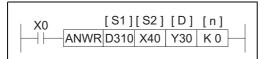

|          | 3 ANWR (FNC 92)                              |       |

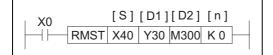

|          | RMST (FNC 93)                                |       |

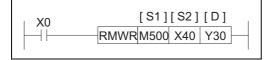

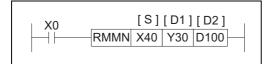

|          | RMMR (FNC 94)                                |       |

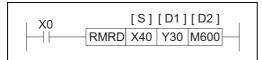

|          | S RMRD (FNC 95)                              |       |

|          | ' RMMN (FNC 96)                              |       |

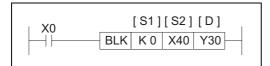

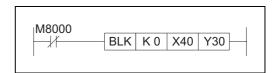

|          | B BLK (FNC 97)                               |       |

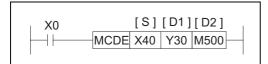

|          | ) MCDF (FNC 98)                              |       |

| 5.11 Floating Point 1 & 2 - Functions 110 to 129                      | 5-119          |

|-----------------------------------------------------------------------|----------------|

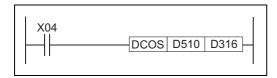

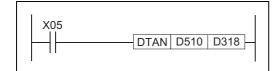

| 5.11.1 ECMP (FNC 110)                                                 |                |

| 5.11.2 EZCP (FNC 111)                                                 |                |

| 5.11.3 EBCD (FNC 118)                                                 |                |

| 5.11.4 EBIN (FNC 119)                                                 |                |

| 5.11.5 EADD (FNC 120)                                                 |                |

| 5.11.6 EAUB (FNC 121)                                                 |                |

| 5.11.7 EMUL (FNC 122)                                                 |                |

| 5.11.8 EDIV (FNC 123)                                                 | 5-125          |

| 5.11.9 ESQR (FNC 127)                                                 |                |

| 5.11.10INT (FNC 129)                                                  | 5-120          |

| 5.12 Trigonometry - FNC 130 to FNC 139                                |                |

| 5.12.1 SIN (FNC 130)                                                  |                |

| 5.12.2 COS (FNC 131)                                                  |                |

| 5.13 Data Operations 2 - FNC 140 to FNC 149                           | 5-130<br>5 122 |

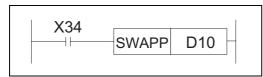

| 5.13.1 SWAP (FNC 147)                                                 | 5 132          |

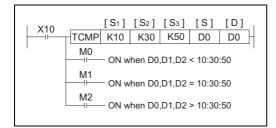

| 5.14 Real Time Clock Control - FNC 160 to FNC 169                     | 5-136          |

| 5.14.1 TCMP (FNC 160)                                                 |                |

| 5.14.2 TZCP (FNC 161)                                                 |                |

| 5.14.3 TADD (FNC 162)                                                 |                |

| 5.14.4 TSUB (FNC 163)                                                 |                |

| 5.14.5 TRD (FNC 166)                                                  |                |

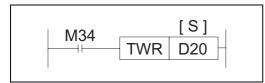

| 5.14.6 TWR (FNC 167)                                                  |                |

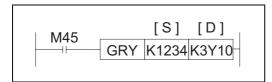

| 5.15 Gray Codes - FNC 170 to FNC 179                                  |                |

| 5.15.1 GRY (FNC 170)                                                  |                |

| 5.15.2 GBIN (FNC 171)                                                 | 5-145          |

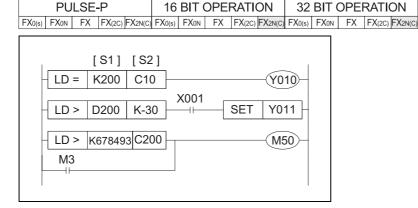

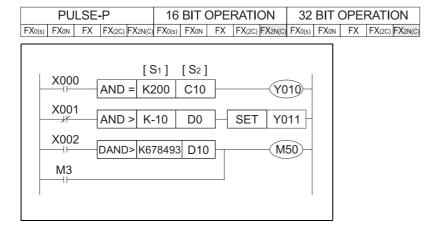

| 5.16 Inline Comparisons - FNC 220 to FNC 249                          | 5-148          |

| 5.16.1 LD compare (FNC 224 to 230)                                    |                |

| 5.16.2 AND compare (FNC 232 to 238)                                   | 5-150          |

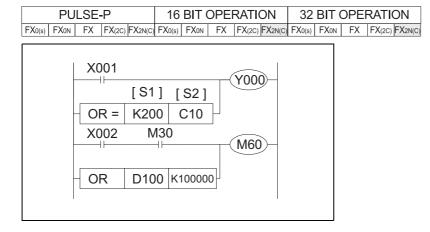

| 5.16.3 OR compare (FNC 240 to 246)                                    | 5-151          |

| 6. Diagnostic Devices                                                 | 6-1            |

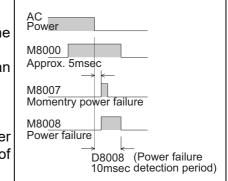

| 6.1 PLC Status (M8000 to M8009 and D8000 to D8009)                    |                |

| 6.2 Clock Devices (M8010 to M8019 and D8000 to D8019)                 |                |

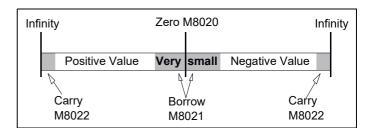

| 6.3 Operation Flags                                                   |                |

| 6.4 PLC Operation Mode (M8030 to M8039 and D8030 to D8039)            |                |

|                                                                       |                |

| 6.5 Step Ladder (STL) Flags (M8040 to M8049 and D8040 to D8049)       |                |

| 6.6 Interrupt Control Flags (M8050 to M8059 and D8050 to D8059)       |                |

| 6.7 Error Detection Devices (M8060 to M8069 and D8060 to D6069)       |                |

| 6.8 Link And Special Operation Devices (M8070 to M8099 and D8070 to D |                |

| 6.9 Miscellaneous Devices (M8100 to M8119 and D8100 to D8119)         |                |

| 6.10 Communication Adapter Devices, i.e. 232ADP, 485ADP               |                |

| 6.11 High Speed Zone Compare Table Comparison Flags                   |                |

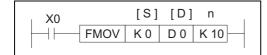

| 6.12 Miscellaneous Devices (M8160 to M8199)                           |                |

| 6.13 Index Registers (D8180 to D8199)                                 |                |

| 6.14 Up/Down Counter Control (M8200 to M8234 and M8200 to D8234)      |                |

| 6.15 High Speed Counter Control (M8235 to M8255 and D8235 to D8255)   | 6-15           |

| n in Euri ( 1000 190100                                               | n-1h           |

| 7. Execution Times And Instructional Hierarchy                             | 7-1              |

|----------------------------------------------------------------------------|------------------|

| 7.1 Basic Instructions                                                     |                  |

| 7.2 Applied Instructions                                                   |                  |

| 7.3 Hierarchical Relationships Of Basic Program Instructions               |                  |

| 7.4 Batch Processing                                                       |                  |

| 7.5 Summary of Device Memory Allocations                                   |                  |

| 7.6 Limits Of Instruction Usage                                            |                  |

| 7.6.1 Instructions Which Can Only Be Used Once In The Main Program Area    |                  |

| 7.6.2 Instructions Which Are Not Suitable For Use With 110V AC Input Units | 7-16             |

| 8. PLC Device Tables                                                       | 8-1              |

| 8.1 Performance Specification Of The FX0 And FX0S                          |                  |

| 8.2 Performance Specification Of The FX0N                                  |                  |

| 8.3 Performance Specification Of The FX (CPU versions 2.0 to 3.06)         |                  |

| 8.4 Performance Specification Of The FX                                    |                  |

| (CPU versions from 3.07) And FX2C (all versions)                           | 8-6              |

| 8.5 Performance Specification Of The FX2N(C)                               |                  |

|                                                                            |                  |

| 9. Assigning System Devices                                                | 9-1              |

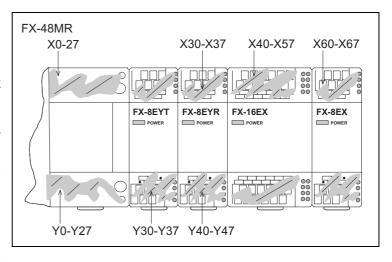

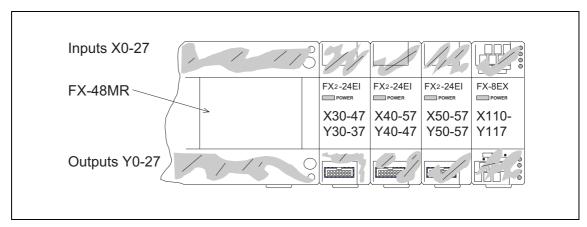

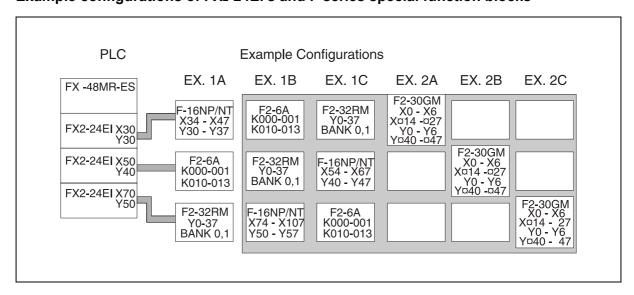

| 9.1 Addressing Extension Modules                                           | 9-1              |

| 9.2 Using The FX2-24EI With F Series Special Function Blocks               |                  |

| 9.2.1 Using the FX2-24EI With A F-16NP/NT                                  |                  |

| 9.2.2 Using the FX2-24EI With A F2-6A                                      |                  |

| 9.2.3 Using the FX2-24EI With A F2-32RM                                    |                  |

| 9.2.4 Using the FX2-24El With A F2-30GM                                    |                  |

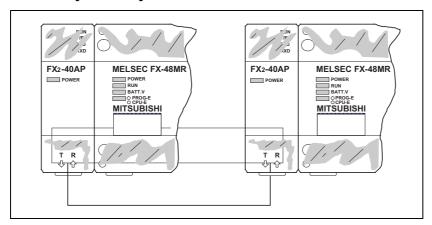

| 9.3 Parallel Link Adapters                                                 |                  |

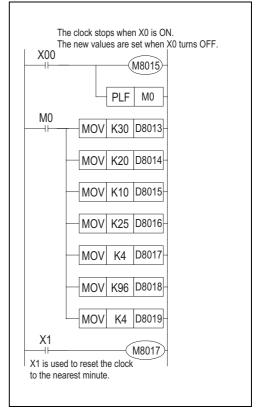

| 9.4 Real Time Clock Function                                               |                  |

| 9.4.1 Setting the real time clock                                          | 9 <del>-</del> 0 |

| 10.Points Of Technique                                                     | 10-1             |

| 10.1 Advanced Programming Points                                           |                  |

| 10.2 Users of DC Powered FX Units                                          |                  |

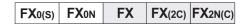

| 10.3 Using The Forced RUN/STOP Flags                                       |                  |

| 10.3.1 A RUN/STOP push button configuration                                | 10-2             |

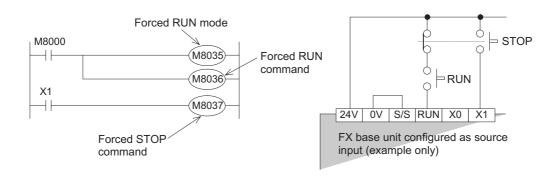

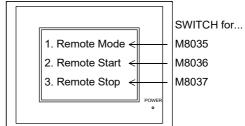

| 10.3.2 Remote RUN/STOP control                                             |                  |

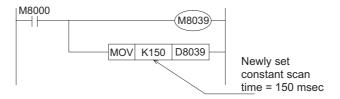

| 10.4 Constant Scan Mode                                                    | 10-4             |

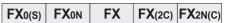

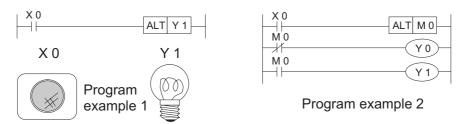

| 10.5 Alternating ON/OFF States                                             | 10-4             |

| 10.6 Using Battery Backed Devices For Maximum Advantage                    | 10-5             |

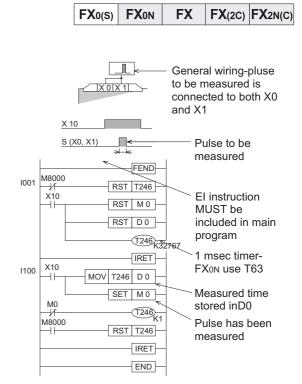

| 10.7 Indexing Through Multiple Display Data Values                         | 10-5             |

| 10.8 Reading And Manipulating Thumbwheel Data                              |                  |

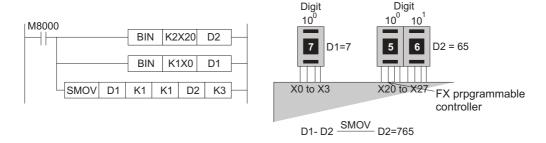

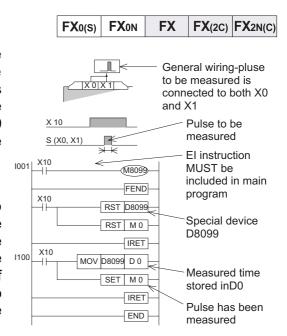

| 10.9 Measuring a High Speed Pulse Input                                    |                  |

| 10.9.1 A 1 msec timer pulse measurement                                    |                  |

| 10.9.2 A 0.1 msec timer pulse measurement                                  |                  |

| 10.10Using The Execution Complete Flag, M8029                              |                  |

| 10.11Creating a User Defined MTR Instruction                               |                  |

| 10.12An Example System Application Using STL And IST Program Control       |                  |

| 10.13Using The PWM Instruction For Motor Control                           |                  |

| 10.14 Communication Format                                                 |                  |

| 10.14.1Specification of the communication parameters:                      |                  |

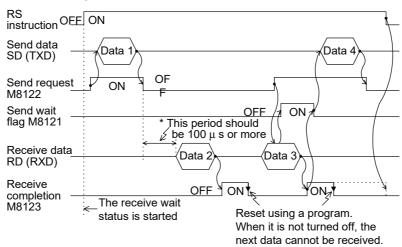

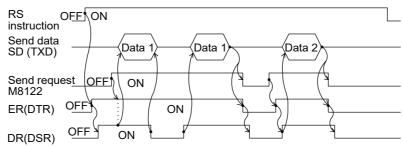

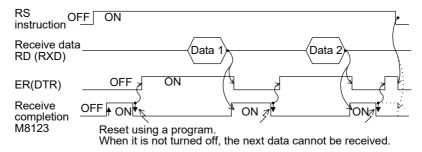

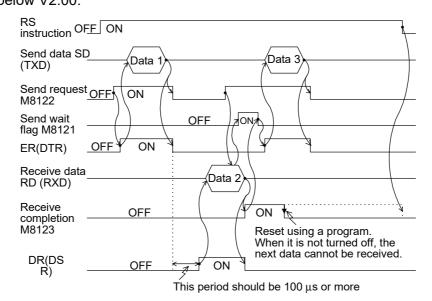

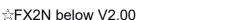

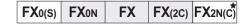

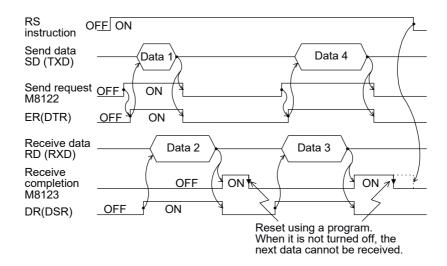

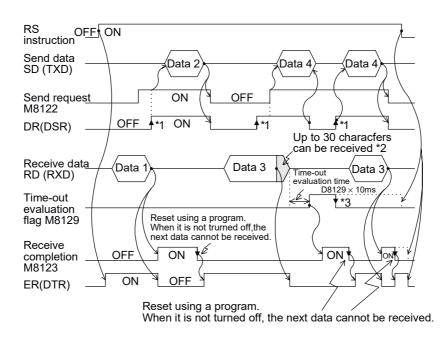

| 10.14.3Timing diagrams for communications:                                 |                  |

| 10.14.48 bit or 16 bit communications.                                     |                  |

www.nicsanat.com 021-87700210

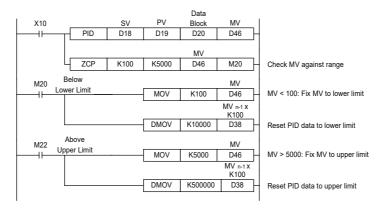

| 10.15PID Programming Techniques             | 10-24 |

|---------------------------------------------|-------|

| 10.15.1Keeping MV within a set range        |       |

| 10.15.2Manual/Automatic change over         |       |

| 10.15.3Using the PID alarm signals          |       |

| 10.15.4Other tips for PID programming       |       |

| 10.16Additional PID functions               |       |

| 10.16.1Output Value range control (S3+1 b5) |       |

| 10.17Pre-tuning operation                   |       |

| 10.17.1Variable Constants                   |       |

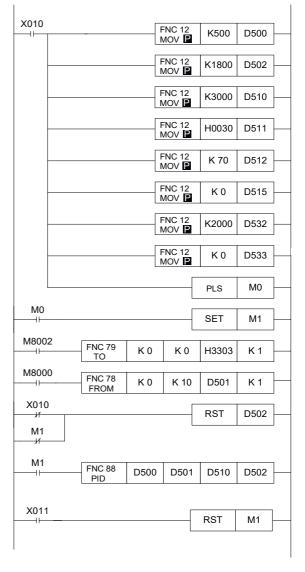

| 10.18Example Autotuning Program             |       |

| 11.Index                                    | 11-1  |

| 11.1 Index                                  |       |

| 11.2 ASCII Character Codes                  |       |

| 11.3 Applied Instruction List               |       |

| 1  | Introduction                |

|----|-----------------------------|

| 2  | Basic Program Instructions  |

| 3  | STL Programming             |

| 4  | Devices in Detail           |

| 5  | Applied Instructions        |

| 6  | Diagnostic Devices          |

| 7  | Instruction Execution Times |

| 8  | PLC Device Tables           |

| 9  | Assigning System Devices    |

| 10 | Points of Technique         |

| 11 | Index                       |

## **Chapter Contents**

| 1. Introduction                                      | 1-1 |

|------------------------------------------------------|-----|

| 1.1 Overview                                         | 1-1 |

| 1.2 What is a ProgrammableController?                |     |

| 1.3 What do You Need to Program a PC?                |     |

| 1.4 CPU version numbers                              | 1-3 |

| 1.4.1 FX0N CPU versions                              | 1-3 |

| 1.4.2 FX and FX2c CPU versions                       | 1-3 |

| 1.5 Special considerations for programming equipment | 1-4 |

| 1.5.1 FX CPU version 3.07 or later and FX2C          |     |

| 1.5.2 FX2N CPU all versions                          | 1-5 |

#### 1. Introduction

#### 1.1 Overview

1) Scope of this manual

This manual gives details on all aspects of operation and programming for FX, FX2C, FX0N, FX0S, FX0, FX2N and FX2NC programmable controllers (PLCs). For all information relating to the PLC hardware and installation, refer to the appropriate manual supplied with the unit.

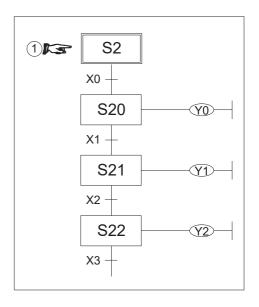

2) How to use this manual

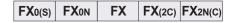

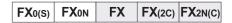

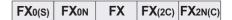

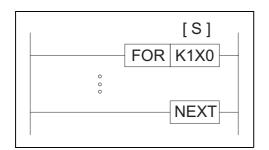

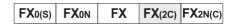

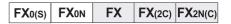

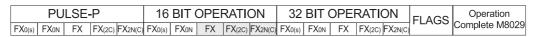

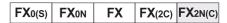

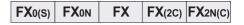

This manual covers all the functions of the highest specification Programmable (Logic) Controller (PLC). For this reason, the following indicator is included in relevant section titles to show which PLCs that section applies to;

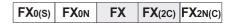

Shaded boxes indicate the applicable PLC type

- "FX0(s)" All FX0 and FX0s PLCs

- "FXON" All FXON PLCs

- "FX" All FX and FX2 PLCs (CPU ver 2.30 or earlier)

- "FX(2C)" All FX and FX2 PLCs (CPU versions 3.07 or later)

- - All FX2c PLCs (see page 1-4)

- "FX2N(C)" All FX2N and FX2NC PLCs

If an indicator box is half shaded, as shown to the left, this means that not all the functions described in the current section apply to that PLC. The text explains in further detail or makes an independent reference.

If there are no indicator boxes then assume the section applies to all PLC types unless otherwise stated.

3) FX family

This is a generic term which is often used to describe all Programmable Controllers without identifying individual types or model names.

- 4) CPU version numbers and programming support

- As Mitsubishi upgrades each model different versions have different capabilities.

- Please refer to section 1.4 for details about version numbers and capabilities.

- Please refer to section 1.5 for details about peripheral support for each model.

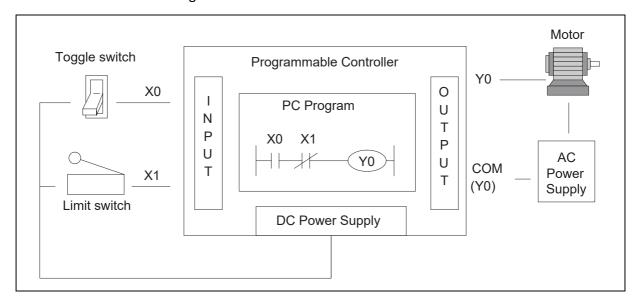

#### 1.2 What is a Programmable Controller?

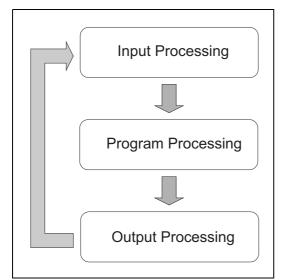

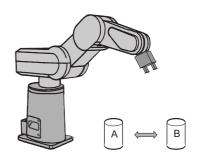

A Programmable Logic Controller (PLC or programmable controller) is a device that a user can program to perform a series or sequence of events. These events are triggered by stimuli (usually called inputs) received at the PLC or through delayed actions such as time delays or counted occur-rences. Once an event triggers, it actuates in the outside world by switching ON or OFF electronic control gear or the physical actuation of devices. A programmable controller will continually 'loop' through its internal 'user defined' program waiting for inputs and giving outputs at the programmed specific times.

#### Note on terminology:

The term programmable controller is a generic word used to bring all the elements making the control system under one descriptive name. Sometimes engineers use the term 'Programmable Logic Controller', 'PLC' or 'programmable controller' to describe the same control system.

The construction of a programmable controller can be broken down into component parts. The element where the program is loaded, stored and processed is often known as the Main Processing Unit or MPU. Other terms commonly heard to describe this device are 'base unit', 'controller' and 'CPU'. The term CPU is a little misleading as todays more advanced products may contain local CPU devices. A Main CPU (or more correctly a Main Processing Unit) controls these local CPUs through a communication network or bus.

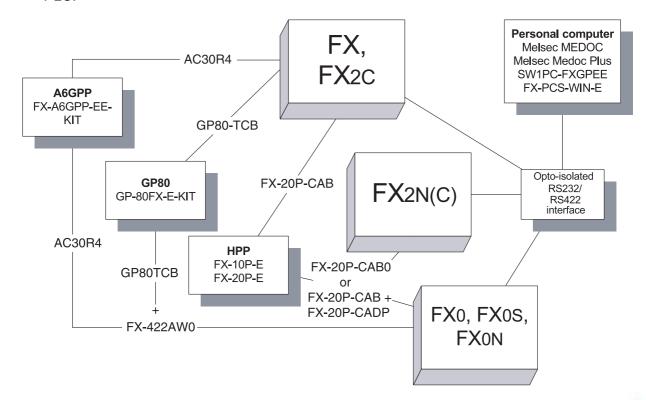

### 1.3 What do You Need to Program a PLC?

A variety of tools are available to program the Mitsubishi FX family of PLCs. Each of these tools can use and access the instructions and devices listed in this manual for the identified PLC.

#### 1.4 **CPU** version numbers

| FX0(S) FX0N FX FX(2C) FX2N(C) |

|-------------------------------|

|-------------------------------|

Over time Mitsubishi adds newer and better features to develop and enhance the products. Because of the nature of PLCs, that can be likened to 'industrial computers', changes sometimes occur within the units main CPU (Central Processing Unit). These changes are similar to those experienced by office and home computer users, that is, going to a version up processor. The following lists identify the CPU versions that had significant upgrades or new functions and features added.

#### 1.4.1 **FX0N CPU versions**

CPU Ver 1.20 The following features were added:

> Software control for protocol 1 and 4 communications with the FX0N-485ADP, 1:N network.

CPU Ver 1.40 The following features were added:

Software control for communications using the FXon-485ADP, peer to peer

#### 1.4.2 FX and FX<sub>2</sub>c CPU versions

**CPU Ver 3.07** The following instructions were added:

> ASCI (FNC82), CCD (FNC84), FLT (FNC49), HEX (FNC83), RS (FNC80), SER (FNC61), SORT (FNC69), SQR (FNC48)

The following instructions were upgraded:

EI (FNC04), BMOV (FNC15), HSCS (FNC53), PLSY (FNC57),

FMOV (FNC16), MEAN (FNC45), ABSD (FNC62), DSW (FNC72), SEGL (74), PR (FNC 77)

The following device ranges were added:

Input and output devices are independently addressable upto 256 points in software. Total combined input and output points (hardware or software) is 256.

Auxiliary relays increased to 1536 points (M0-M1535)

Data registers increased to 1000 points (D0-D999)

Optional RAM File Registers added, 2000 points (D6000 -D7999)

Pointers increased to 128 points (P0 - P127)

**CPU Ver 3.11** The following instructions were added:

PID (FNC88)

CPU Ver 3.2 The following features were added:

> Software control for protocol 4 communications with the FX-485ADP, 1:N network.

**CPU Ver 3.30** The following features were added:

> Software control for protocol 1 communications with the FX-485ADP, 1:N network.

The following instructions were phased out (removed):

ANRD (FNC91), ANWR (FNC92), BLK (FNC97), MCDE (FNC98), MNET (FNC90)

#### 1.5 Special considerations for programming equipment

#### 1.5.1 FX CPU version 3.07 or later and FX<sub>2</sub>c

Programming tools operating old system software can not access the new features added to the FX CPU from version 3.07 (and available on all FX<sub>2</sub>C units). However, programming certain 'standard' applied instructions in conjunction with special auxiliary coils (M coils) can achieve the same 'effective instruction' as the new instructions. The following tables identify which version of peripheral software will work directly with all of the 'new' features and which peripheral software versions require use of modified instructions.

| Peripherals Table          |                 |                                      |                                   |  |  |  |

|----------------------------|-----------------|--------------------------------------|-----------------------------------|--|--|--|

|                            |                 | System software version which will   |                                   |  |  |  |

| Description                | Model Number    | require the use of auxiliary M coils | program all instructions directly |  |  |  |

| Hand held programmer (HHP) | FX-10P-E        | V 1.10                               | from V 2.00                       |  |  |  |

| HHP cassette               | FX-20P-MFXA-E   | V 1.20                               | from V 2.00                       |  |  |  |

| Programming                | FX-PCS/AT-E-KIT | V 1.01                               | from V 2.00                       |  |  |  |

| software                   | FX-A6GPP-E-KIT  | V 1.00                               | from V 2.00                       |  |  |  |

|                            | FX-10DU-E       | V 1.10                               | from V 2.00                       |  |  |  |

| Data access units          | FX-20DU-E       | V 1.10                               | from V 2.00                       |  |  |  |

|                            | Other DU units  |                                      | from V 1.00                       |  |  |  |

| Existin             | Existing Instruction And Special M Coil Combination To Mimic The Operation Of The Identified Instruction |                  |                                |          |            |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------|------------------|--------------------------------|----------|------------|--|--|--|

| E                   | xisting FX inst                                                                                          | ruction          | used to mimic the operation of |          |            |  |  |  |

| Mnemonic FNC number |                                                                                                          | Modifying M coil | Mimicked instruction           | Mnemonic | FNC Number |  |  |  |

| MOV                 | 12                                                                                                       | M8190            | Square root                    | SQR      | 48         |  |  |  |

| MOV                 | 12                                                                                                       | M8191            | Float                          | FLT      | 49         |  |  |  |

| RAMP                | 67                                                                                                       | M8193            | Data search                    | SER      | 61         |  |  |  |

| RAMP                | 67                                                                                                       | M8194            | RS232 instruction              | RS       | 80         |  |  |  |

| FMOV                | 16                                                                                                       | M8196            | Hex to ASCII conversion        | ASCI     | 82         |  |  |  |

| FMOV                | 16                                                                                                       | M8197            | ASCII to Hex conversion        | HEX      | 83         |  |  |  |

| FMOV                | 16                                                                                                       | M8195            | Sum check                      | CCD      | 84         |  |  |  |

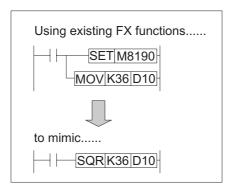

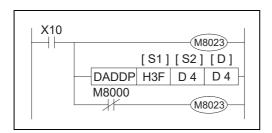

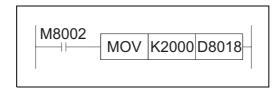

#### **Example usage**

This format is very important for the instruction to operate correctly. The user must program the 'mimic' instruction with the modifying M coil in a SET instruction immediately before the instruction to be modified.

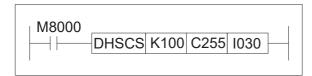

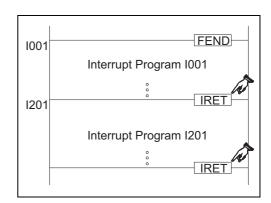

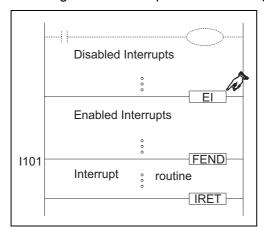

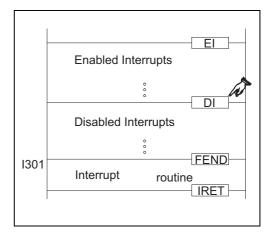

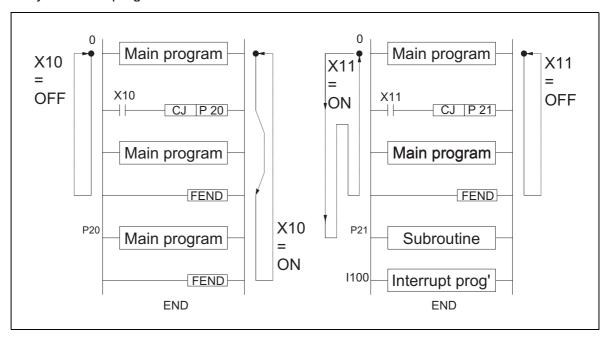

Using the new Interrupt Pointers:

To program new Interrupt Pointers I010 through I060 in to the HSCS (FNC 53) instruction with older programming equipment, substitute the following special M codes for the appropriate Interrupt Pointer; see the table right.

| Existing Instruction And Special M Coil<br>Combination To Mimic The Operation<br>Of The Identified Interrupt pointer |                   |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|

| Existing Auxiliary Coil used to replace the identified Interrupt Pointer                                             | Interrupt Pointer |  |  |  |

| M8181                                                                                                                | I010              |  |  |  |

| M8182                                                                                                                | 1020              |  |  |  |

| M8183                                                                                                                | 1030              |  |  |  |

| M8184                                                                                                                | 1040              |  |  |  |

| M8185                                                                                                                | 1050              |  |  |  |

| M8186                                                                                                                | 1060              |  |  |  |

Using M8198 with the BMOV instruction:

With old software and peripherals, file registers can not be used as a destination device in the BMOV (FNC 15) instruction. To BMOV data into file registers with old equipment set special M coil M8198 on. This switches the source and destination parameters; i.e., the source is then treated as the destination and the destination becomes the source.

General note:

Ignore the special programming techniques identified in this section if using updated programming software or peripherals; then normal operation, as identified in the following sections, will apply.

#### 1.5.2 FX2N(C) CPU all versions

www.nicsanat.com 021-87700210

The introduction of this CPU provides the FX user with many new devices and instructions. To use the full features of the FX2N(C) units the user must upgrade older software and hardware programming tools.

However, because of the downward compatibility of the FX2N(C), it is not necessary to upgrade existing programming tools for use with FX2N(C) units up to the equivalent functionality of FX CPU ver 3.30 units.

| Peripherals Table          |                    |                                                                   |  |  |  |  |

|----------------------------|--------------------|-------------------------------------------------------------------|--|--|--|--|

| Description                | Model Number       | System software version with full support for FX <sub>2N(c)</sub> |  |  |  |  |

| Hand held programmer (HHP) | FX-10P-E           | from V 3.00                                                       |  |  |  |  |

| HHP cassette               | FX-20P-MFXA-E      | from V 3.00                                                       |  |  |  |  |

|                            | FX-10DU-E          | from V 4.00                                                       |  |  |  |  |

|                            | FX-20DU-E          | Supports up to FX devices only                                    |  |  |  |  |

|                            | FX-25DU-E          | from V 2.00                                                       |  |  |  |  |

| Data access units          | FX-30DU-E          | from V 3.00                                                       |  |  |  |  |

| Data access units          | FX-40DU-E(S)       | Supports up to FX devices only                                    |  |  |  |  |

|                            | FX-40DU-TK-ES      | from V 3.00                                                       |  |  |  |  |

|                            | FX-50DU-TK(S)-E    | from V 2.10                                                       |  |  |  |  |

|                            | F940GOT-SWD(LWD)-E | All versions                                                      |  |  |  |  |

## **MEMO**

| 1  | Introduction                |

|----|-----------------------------|

| 2  | Basic Program Instructions  |

| 3  | STL Programming             |

| 4  | Devices in Detail           |

| 5  | Applied Instructions        |

| 6  | Diagnostic Devices          |

| 7  | Instruction Execution Times |

| 8  | PLC Device Tables           |

| 9  | Assigning System Devices    |

| 10 | Points of Technique         |

| 11 | Index                       |

## **Chapter Contents**

| 2. Basic Program Instructions                      | 2-1  |

|----------------------------------------------------|------|

| 2.1 What is a Program?                             | 2-1  |

| 2.2 Outline of Basic Devices Used in Programming   |      |

| 2.3 How to Read Ladder Logic                       | 2-2  |

| 2.4 Load, Load Inverse                             |      |

| 2.5 Out                                            |      |

| 2.5.1 Timer and Counter Variations                 |      |

| 2.5.2 Double Coil Designation                      |      |

| 2.6 And, And Inverse                               | 2-6  |

| 2.7 Or, Or Inverse                                 | 2-7  |

| 2.8 Load Pulse, Load Trailing Pulse                | 2-8  |

| 2.9 And Pulse, And Trailing Pulse                  | 2-9  |

| 2.10 Or Pulse, Or Trailing Pulse                   | 2-10 |

| 2.11 Or Block                                      | 2-11 |

| 2.12 And Block                                     | 2-12 |

| 2.13 MPS, MRD and MPP                              | 2-13 |

| 2.14 Master Control and Reset                      | 2-15 |

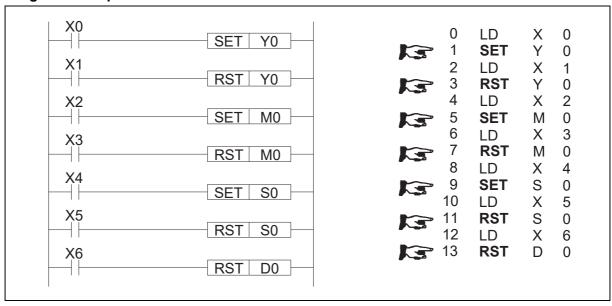

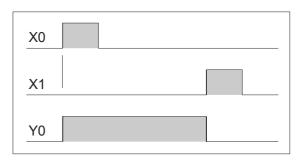

| 2.15 Set and Reset                                 | 2-17 |

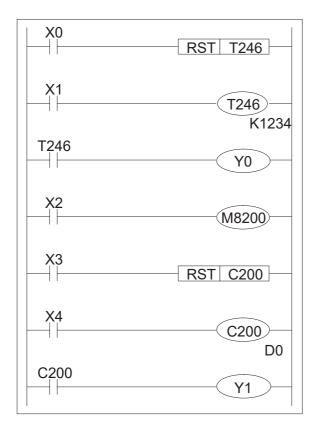

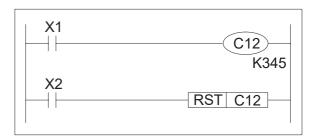

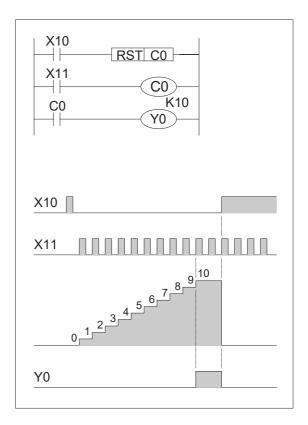

| 2.16 Timer, Counter(Out & Reset)                   | 2-18 |

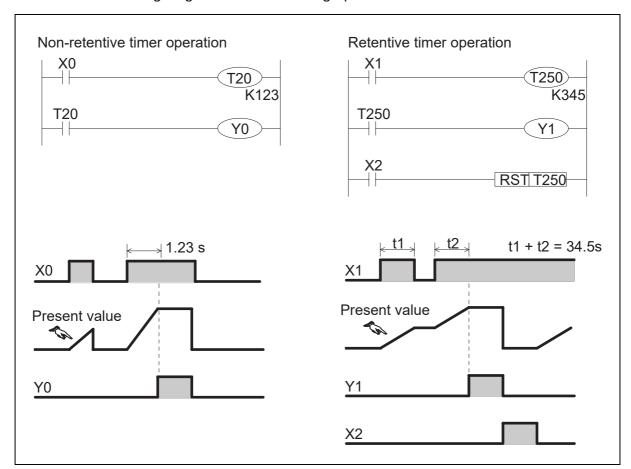

| 2.16.1 Basic Timers, Retentive Timers And Counters | 2-18 |

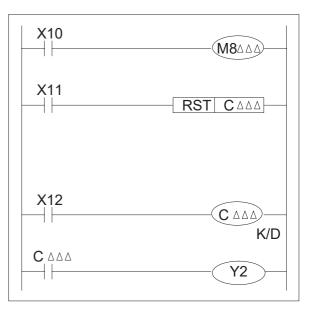

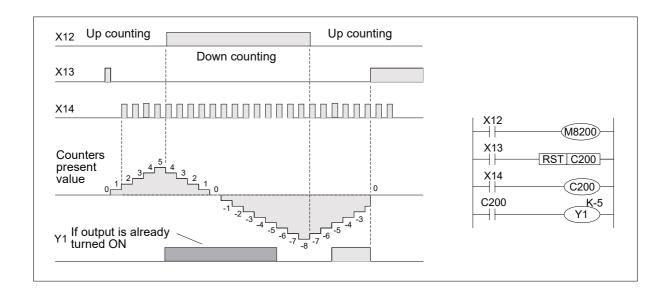

| 2.16.2 Normal 32 bit Counters                      | 2-19 |

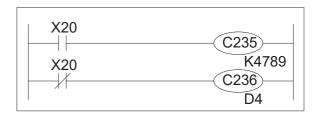

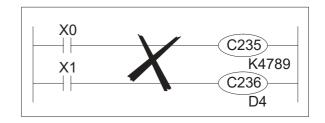

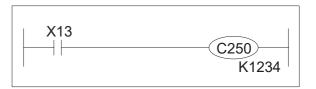

| 2.16.3 High Speed Counters                         |      |

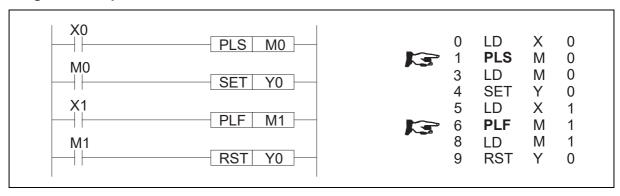

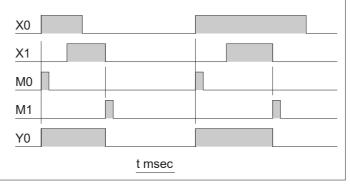

| 2.17 Leading and Trailing Pulse                    |      |

| 2.18 Inverse                                       |      |

| 2.19 No Operation                                  |      |

| 2.20 End                                           | 2-23 |

### 2. Basic Program Instructions

#### 2.1 What is a Program?

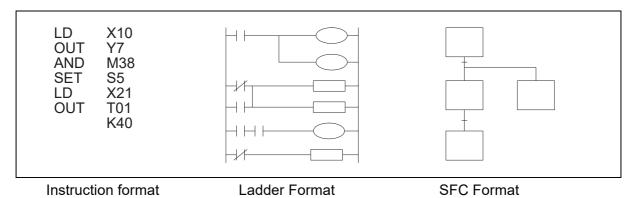

A program is a connected series of instructions written in a language that the PLC can understand. There are three forms of program format; instruction, ladder and SFC/STL. Not all programming tools can work in all programming forms. Generally hand held programming panels only work with instruction format while most graphic programming tools will work with both instruction and ladder format. Specialist programming software will also allow SFC style programming.

### 2.2 Outline of Basic Devices Used in Programming

There are six basic programming devices. Each device has its own unique use. To enable quick and easy identification each device is assigned a single reference letter;

- X: This is used to identify all direct, physical inputs to the PLC.

- Y: This is used to identify all direct, physical outputs from the PLC.

- T: This is used to identify a timing device which is contained within the PLC.

- C: This is used to identify a counting device which is contained within the PLC.

- M and S: These are used as internal operation flags within the PLC.

All of the devices mentioned above are known as 'bit devices'. This is a descriptive title telling the user that these devices only have two states; ON or OFF, 1 or 0.

#### **Detailed device information:**

• Chapter 4 contains this information in detail. However, the above is all that is required for the rest of this chapter.

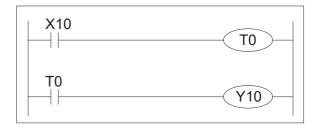

#### 2.3 How to Read Ladder Logic

Ladder logic is very closely associated to basic relay logic. There are both contacts and coils that can be loaded and driven in different configurations. However, the basic principle remains the same.

A coil drives direct outputs of the PLC (ex. a Y device) or drives internal timers, counters or flags (ex. T, C, M and S devices). Each coil has associated contacts. These contacts are available in both "normally open" (NO) and "normally closed" (NC) configurations.

The term "normal(ly)" refers to the status of the contacts when the coil is not energized. Using a relay analogy, when the coil is OFF, a NO contact would have no current flow, that is, a load being supplied through a NO contact would not operate. However, a NC contact would allow current to flow, hence the connected load would be active.

Activating the coil reverses the contact status, that is, the current would flow in a NO contact and a NC contact would inhibit the flow.

Physical inputs to the PLC (X devices) have no programmable coil. These devices may only be used in a contact format (NO and NC types are available).

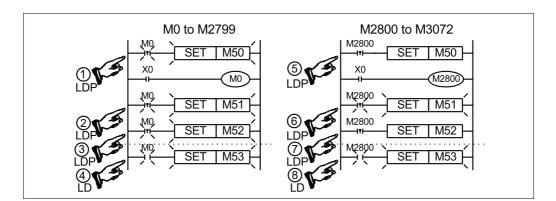

#### **Example:**

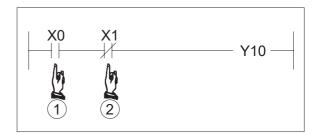

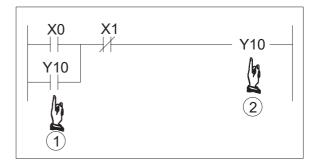

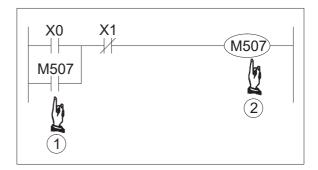

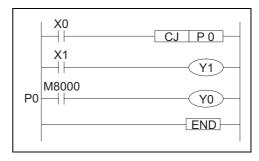

Because of the close relay association, ladder logic programs can be read as current flowing from the left vertical line to the right vertical line. This current must pass through a series of contact representations such as X0 and X1 in order to switch the output coil Y0 ON. Therefore, in the example shown, switching X0 ON causes the output Y0 to also switch ON. If however, the limit switch X1 is activates, the output Y0 turns OFF. This is because the connection between the left and the right vertical lines breaks so there is no current flow.

#### 2.4 Load, Load Inverse

| FX0(S) | FXon | FX | <b>FX</b> (2C) | FX <sub>2</sub> N(C) |

|--------|------|----|----------------|----------------------|

| (-)    |      |    |                |                      |

| Mnemonic              | Function                                                             | Format | Devices          | Program steps |

|-----------------------|----------------------------------------------------------------------|--------|------------------|---------------|

| LD<br>(LoaD)          | Initial logical<br>operation contact<br>type NO<br>(normally open)   |        | X, Y, M, S, T, C | 1             |

| LDI<br>(LoaD Inverse) | Initial logical<br>operation contact<br>type NC<br>(normally closed) |        | X, Y, M, S, T, C | 1             |

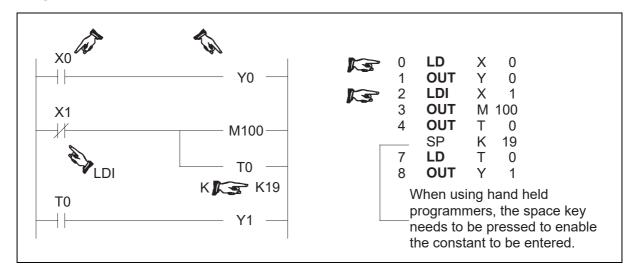

#### Program example:

#### Basic points to remember:

- Connect the LD and LDI instructions directly to the left hand bus bar.

- Or use LD and LDI instructions to define a new block of program when using the ORB and ANB instructions (see later sections).

#### The OUT instruction:

• For details of the OUT instruction (including basic timer and counter variations) please see over the following page.

#### 2.5 Out

|  | <b>FX</b> 0(S) | FX <sub>0N</sub> | FX | <b>FX</b> (2C) | FX2N(C) |  |

|--|----------------|------------------|----|----------------|---------|--|

|--|----------------|------------------|----|----------------|---------|--|

| Mnemonic     | Function                                | Format | Devices       | Program steps                                                               |

|--------------|-----------------------------------------|--------|---------------|-----------------------------------------------------------------------------|

| OUT<br>(OUT) | Final logical operation type coil drive |        | Y, M, S, T, C | Y, M:1<br>S, special M<br>coils: 2<br>T:3<br>C (16 bit): 3<br>C (32 bit): 5 |

Basic points to remember:

- Connect the OUT instruction directly to the right hand bus bar.

- It is not possible to use the OUT instruction to drive 'X' type input devices.

- It is possible to connect multiple OUT instructions in parallel (for example see the previous page; M100/T0 configuration)

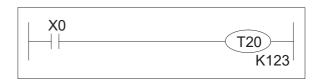

#### 2.5.1 Timer and Counter Variations

When configuring the OUT instruction for use as either a timer (T) or counter (C) a constant must also be entered. The constant is identified by the letter "K" (for example see previous page; T0 K19).

In the case of a timer, the constant "K" holds the duration data for the timer to operate, i.e. if a 100 msec timer has a constant of "K100" it will be (1005 100 msec) 10 seconds before the timer coil activates.

With counters, the constant identifies how many times the counter must be pulsed or triggered before the counter coil activates. For example, a counter with a constant of "8" must be triggered 8 times before the counter coil finally energizes.

The following table identifies some basic parameter data for various timers and counters;

| Timer/Counter  | Setting constant K              | Actual setting                  | Program steps |  |

|----------------|---------------------------------|---------------------------------|---------------|--|

| 1 msec Timer   |                                 | 0.001 to 32.767 sec             |               |  |

| 10 msec Timer  | 1 to 32,767                     | 0.01 to 327.67 sec              | 2             |  |

| 100 msec Timer |                                 | 0.1 to 3276.7 sec               |               |  |

| 16 bit Counter | 1 to 32,767                     | 1 to 32,767                     |               |  |

| 32 bit Counter | -2,147,483,648 to 2,147,483,647 | -2,147,483,648 to 2,147,483,647 | 5             |  |

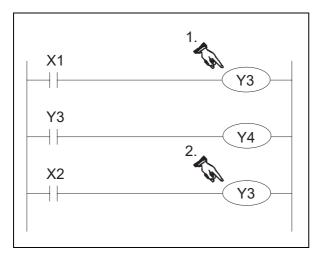

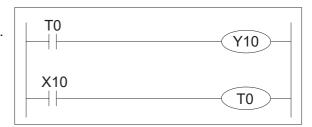

#### 2.5.2 Double Coil Designation

Double or dual coiling is not a recommended practice. Using multiple output coils of the same device can cause the program operation to become unreliable. The example program shown opposite identifies a double coil situation; there are two Y3 outputs. The following sequence of events will occur when inputs X1 = ON and X2 = OFF;

- 1. The first Y3 tuns ON because X1 is ON. The contacts associated with Y3 also energize when the coil of output Y3 energizes. Hence, output Y4 turns ON.

- 2. The last and most important line in this program looks at the status of input X2.

If this is NOT ON then the second Y3 coil does NOT activate. Therefore the status of the Y3 coil updates to reflect this new situation, i.e. it turns OFF. The final outputs are then Y3 = OFF and Y4 = ON.

#### Use of dual coils:

Always check programs for incidents of dual coiling. If there are dual coils the program will not operate as expected - possibly resulting in unforeseen physical

#### The last coil effect:

In a dual coil designation, the coil operation designated last is the effective coil. That

is, it is the status of the previous coil that dictates the behavior at the current point in

the program.

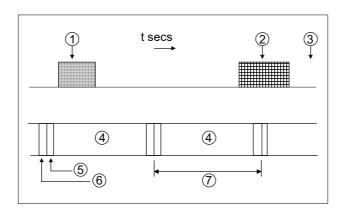

#### Input durations:

The ON or OFF duration of the PLC inputs must be longer than the operation cycle time of the PLC.

Taking a 10 msec (standard input filter) response delay into account, the ON/OFF duration must be longer than 20 msec if the operation cycle (scan time) is 10 msec.

Therefore, in this example, input pulses of more than 25Hz (1sec/(20msec ON + 20msec OFF)) cannot be sensed.

There are applied instructions provided to handle such high speed input requests.

- ①: Input ON state NOT recognized

- ②: Input ON state recognized

- ③: Input OFF state NOT recognized

- ①: 1 program processing

- ⑤: Input processing

- 6: Output processing

- ②: A full program scan/operation cycle

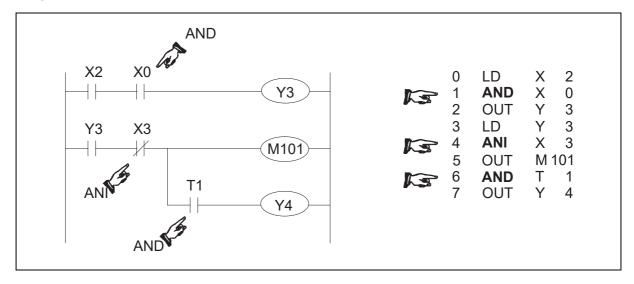

#### 2.6 And, And Inverse

| FX0(S) FX0N FX FX(2C) FX2N( |

|-----------------------------|

|-----------------------------|

| Mnemonic             | Function                                                 | Format | Devices          | Program steps |

|----------------------|----------------------------------------------------------|--------|------------------|---------------|

| AND<br>(AND)         | Serial connection<br>of NO (normally<br>open) contacts   |        | X, Y, M, S, T, C | 1             |

| ANI<br>(AND Inverse) | Serial connection<br>of NC (normally<br>closed) contacts |        | X, Y, M, S, T, C | 1             |

#### Program example:

#### Basic points to remember:

- Use the AND and ANI instructions for serial connection of contacts. As many contacts as required can be connected in series (see following point headed "Peripheral limitations").

- The output processing to a coil, through a contact, after writing the initial OUT instruction is called a "follow-on" output (for an example see the program above; OUT Y4). Follow-on outputs are permitted repeatedly as long as the output order is correct.

#### **Peripheral limitations:**

The PLC has no limit to the number of contacts connected in series or in parallel.

However, some programming panels, screens and printers will not be able to display

or print the program if it exceeds the limit of the hardware. It is preferable for each

line or rung of ladder program to contain up to a maximum of 10 contacts and 1 coil.

Also, keep the number of follow-on outputs to a maximum of 24.

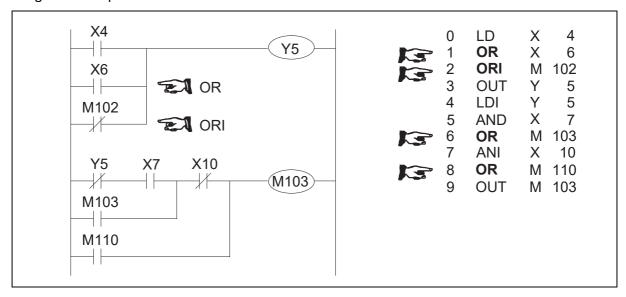

#### 2.7 Or, Or Inverse

| FX0(S) FX0N FX FX(2C) FX2N(C |

|------------------------------|

|------------------------------|

| Mnemonic            | Function                                                      | Format | Devices          | Program steps |

|---------------------|---------------------------------------------------------------|--------|------------------|---------------|

| OR<br>(OR)          | Parallel<br>connection of NO<br>(normally open)<br>contacts   |        | X, Y, M, S, T, C | 1             |

| ORI<br>(OR Inverse) | Parallel<br>connection of NC<br>(normally closed)<br>contacts |        | X, Y, M, S, T, C | 1             |

#### Program example:

#### Basic points to remember:

- Use the OR and ORI instructions for parallel connection of contacts. To connect a block that contains more than one contact connected in series to another circuit block in parallel, use an ORB instruction.

- Connect one side of the OR/ORI instruction to the left hand bus bar.

#### **Peripheral limitations:**

The PLC has no limit to the number of contacts connected in series or in parallel.

However, some programming panels, screens and printers will not be able to display

or print the program if it exceeds the limit of the hardware. It is preferable for each

line or rung of ladder program to contain up to a maximum of 10 contacts and 1 coil.

Also keep number of follow-on outputs to a maximum of 24.

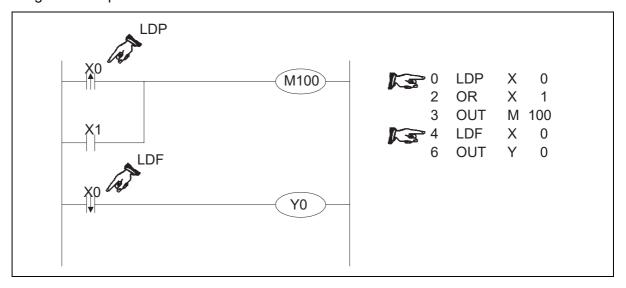

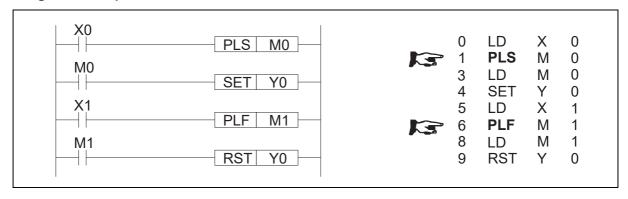

### 2.8 Load Pulse, Load Trailing Pulse

| FX0(S) FX | N FX | FX(2C) | FX2N(C) |

|-----------|------|--------|---------|

|-----------|------|--------|---------|

| Mnemonic                       | Function                                                         | Format   | Devices          | Program steps |

|--------------------------------|------------------------------------------------------------------|----------|------------------|---------------|

| LDP<br>(LoaDPulse)             | Initial logical operation - Rising edge pulse                    | <b>├</b> | X, Y, M, S, T, C | 2             |

| LDF<br>(LoaD Falling<br>pulse) | Initial logical<br>operation Falling<br>/ trailing edge<br>pulse |          | X, Y, M, S, T, C | 2             |

#### Program example:

#### Basic points to remember:

- Connect the LDP and LDF instructions directly to the left hand bus bar.

- Or use LDP and LDF instructions to define a new block of program when using the ORB and ANB instructions (see later sections).

- LDP is active for one program scan after the associated device switches from OFF to ON.

- LDF is active for one program scan after the associated device switches from ON to OFF.

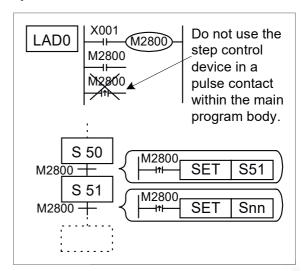

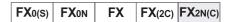

#### Single Operation flags M2800 to M3071:

- The pulse operation instructions, when used with auxiliary relays M2800 to M3071, only activate the first instruction encountered in the program scan, after the point in the program where the device changes. Any other pulse operation instructions will remain inactive.

- This is useful for use in STL programs (see chapter 3) to perform single step operation using a single device.

- Any other instructions (LD, AND, OR, etc.) will operate as expected.

For more details please see page 4-5.

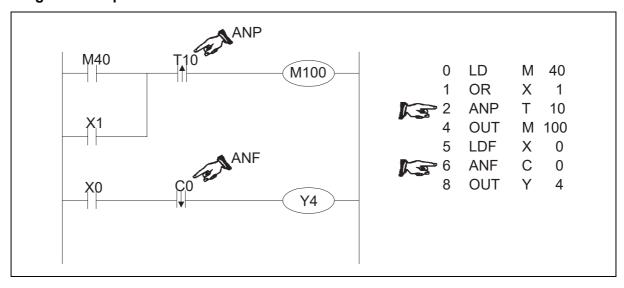

#### 2.9 And Pulse, And Trailing Pulse

| Mnemonic                      | Function                                                    | Format | Devices          | Program steps |

|-------------------------------|-------------------------------------------------------------|--------|------------------|---------------|

| ANP<br>(ANd Pulse)            | Serial connection of Rising edge pulse                      |        | X, Y, M, S, T, C | 2             |

| ANF<br>(ANd Falling<br>pulse) | Serial connection<br>of Falling /<br>trailing edge<br>pulse |        | X, Y, M, S, T, C | 2             |

#### Program example:

#### Basic points to remember:

- Use the ANDP and ANDF instructions for the serial connection of pulse contacts.

- Usage is the same as for AND and ANI; see earlier.

- ANP is active for one program scan after the associated device switches from OFF to ON.

- ANF is active for one program scan after the associated device switches from ON to OFF.

#### Single operation flags M2800 to M3071:

When used with flags M2800 to M3071 only the first instruction will activate. For details see page 2-8

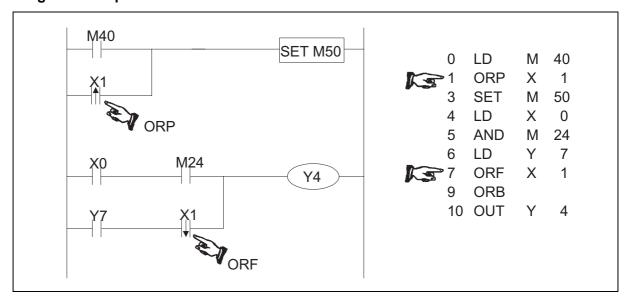

#### 2.10 Or Pulse, Or Trailing Pulse

| Mnemonic                     | Function                                                      | Format | Devices          | Program steps |

|------------------------------|---------------------------------------------------------------|--------|------------------|---------------|

| ORP<br>(OR Pulse)            | Parallel connection of Rising edge pulse                      |        | X, Y, M, S, T, C | 2             |

| ORF<br>(OR Falling<br>pulse) | Parallel<br>connection of<br>Falling / trailing<br>edge pulse |        | X, Y, M, S, T, C | 2             |

#### Program example:

#### Basic points to remember:

- Use the ORP and ORF instructions for the parallel connection of pulse contacts.

- Usage is the same as for OR and ORI; see earlier.

- ORP is active for one program scan after the associated device switches from OFF to ON.

- ORF is active for one program scan after the associated device switches from ON to OFF.

#### Single operation flags M2800 to M3071:

When used with flags M2800 to M3071 only the first instruction will activate. For details see page 2-8

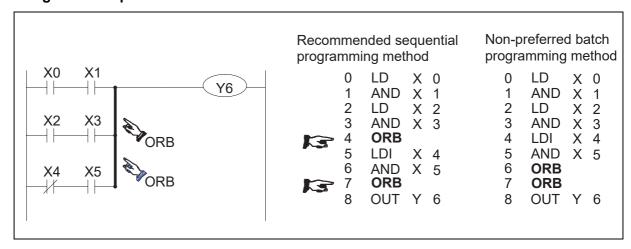

#### 2.11 Or Block

| FX0(S) FX0N | FX | <b>FX</b> (2C) | FX2N(C) |

|-------------|----|----------------|---------|

|-------------|----|----------------|---------|

| Mnemonic          | Function                                         | Format | Devices | Program steps |

|-------------------|--------------------------------------------------|--------|---------|---------------|

| ORB<br>(OR Block) | Parallel connection of multiple contact circuits |        | N/A     | 1             |

### Program example:

#### Basic points to remember:

- An ORB instruction is an independent instruction and is not associated with any device number.

- Use the ORB instruction to connect multi-contact circuits (usually serial circuit blocks) to the preceding circuit in parallel. Serial circuit blocks are those in which more than one contact connects in series or the ANB instruction is used.

- To declare the starting point of the circuit block use a LD or LDI instruction. After completing the serial circuit block, connect it to the preceding block in parallel using the ORB instruction.

#### **Batch processing limitations:**

• When using ORB instructions in a batch, use no more than 8 LD and LDI instructions in the definition of the program blocks (to be connected in parallel). Ignoring this will result in a program error (see the right most program listing).

## Sequential processing limitations:

There are no limitations to the number of parallel circuits when using an ORB instruction in the sequential processing configuration (see the left most program listing).

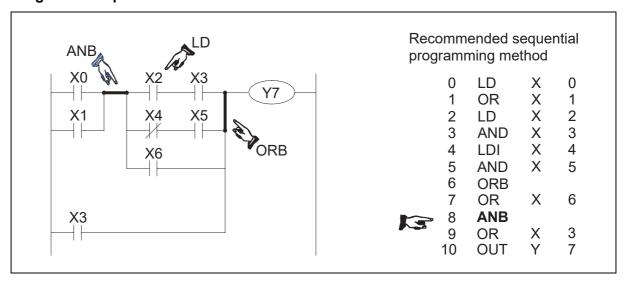

#### 2.12 And Block

| Mnemonic           | Function                                        | Format | Devices | Program steps |

|--------------------|-------------------------------------------------|--------|---------|---------------|

| ANB<br>(ANd Block) | Serial connection of multiple parallel circuits |        | N/A     | 1             |

### Program example:

#### Basic points to remember:

- An ANB instruction is an independent instruction and is not associated with any device number

- Use the ANB instruction to connect multi-contact circuits (usually parallel circuit blocks) to the preceding circuit in series. Parallel circuit blocks are those in which more than one contact connects in parallel or the ORB instruction is used.

- To declare the starting point of the circuit block, use a LD or LDI instruction. After completing the parallel circuit block, connect it to the preceding block in series using the ANB instruction.

## **Batch processing limitations:**

When using ANB instructions in a batch, use no more than 8 LD and LDI instructions in the definition of the program blocks (to be connected in parallel). Ignoring this will result in a program error (see ORB explanation for example).

## Sequential processing limitations:

• It is possible to use as many ANB instructions as necessary to connect a number of parallel circuit blocks to the preceding block in series (see the program listing).

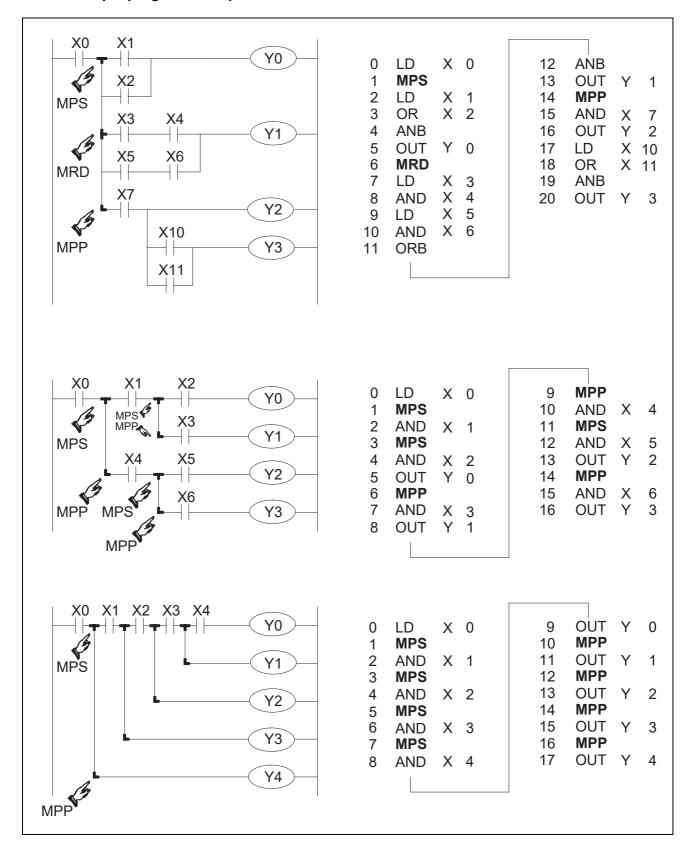

## 2.13 MPS, MRD and MPP

| Mnemonic             | Function                                                 | Format | Devices | Program steps |

|----------------------|----------------------------------------------------------|--------|---------|---------------|

| MPS<br>(Point Store) | Stores the current result of the internal PLC operations | MPS    | N/A     | 1             |

| MRD<br>(Read)        | Reads the current result of the internal PLC operations  | MRD    | N/A     | 1             |

| MPP<br>(PoP)         | Pops (recalls and removes) the currently stored result   | MPP    | N/A     | 1             |

#### Basic points to remember:

- Use these instructions to connect output coils to the left hand side of a contact.

Without these instructions connections can only be made to the right hand side of the last contact.

- MPS stores the connection point of the ladder circuit so that further coil branches can recall the value later.

- MRD recalls or reads the previously stored connection point data and forces the next contact to connect to it.

- MPP pops (recalls and removes) the stored connection point. First, it connects the next contact, then it removes the point from the temporary storage area.

- For every MPS instruction there MUST be a corresponding MPP instruction.

- The last contact or coil circuit must connect to an MPP instruction.

- At any programming step, the number of active MPS-MPP pairs must be no greater than 11.

## MPS, MRD and MPP usage:

- When writing a program in ladder format, programming tools automatically add all MPS, MRD and MPP instructions at the program conversion stage. If the generated instruction program is viewed, the MPS, MRD and MPP instructions are present.

- When writing a program in instruction format, it is entirely down to the user to enter all relevant MPS, MRD and MPP instructions as required.

## Multiple program examples:

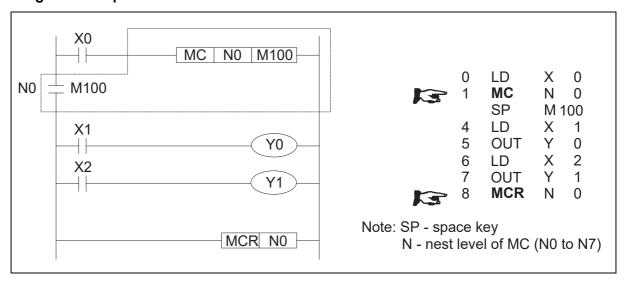

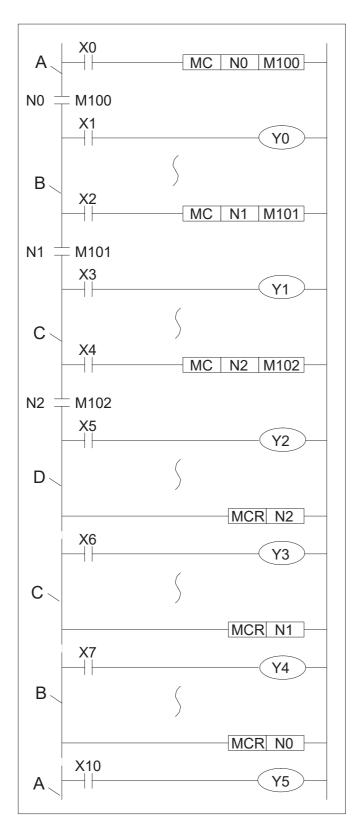

#### 2.14 Master Control and Reset

| Mnemonic                         | Function                                          | Format | Devices                                                                           | Program steps |

|----------------------------------|---------------------------------------------------|--------|-----------------------------------------------------------------------------------|---------------|

| MC<br>(Master<br>Control)        | Denotes the start<br>of a master control<br>block | → MC N | Y, M (no special<br>M coils allowed)<br>N denotes the<br>nest level (N0 to<br>N7) | 3             |

| MCR<br>(Master<br>Control Reset) | Denotes the end of a master control block         | MCR N  | N denotes the nest level (N0 to N7) to be reset.                                  | 2             |

#### Program example:

#### Basic points to remember:

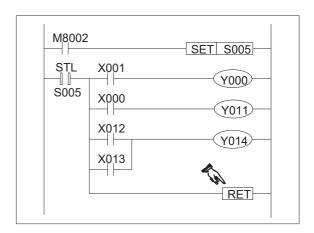

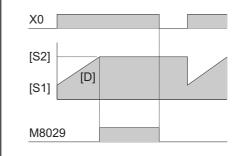

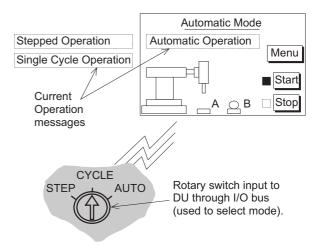

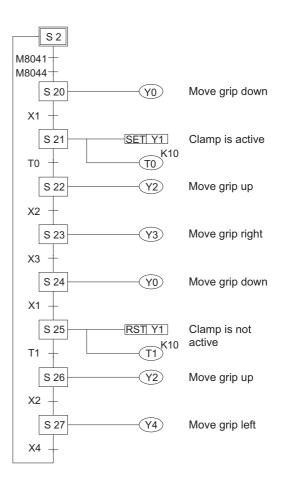

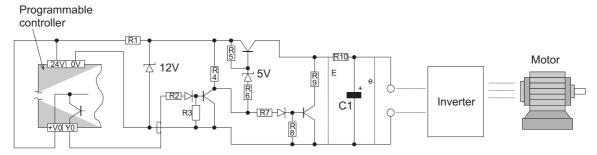

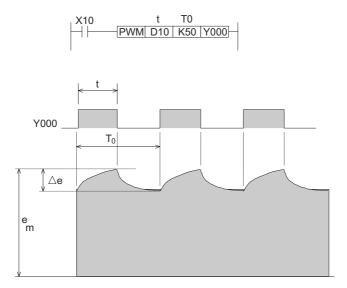

- After the execution of an MC instruction, the bus line (LD, LDI point) shifts to a point after the MC instruction. An MCR instruction returns this to the original bus line.